# Nanostrutture su substrati di silicio per celle fotovoltaiche di nuova generazione

A. Nottola, S. Tirelli, G. Prati, L.V. Mercaldo, M. Izzi, P. Delli Veneri

## NANOSTRUTTURE SU SUBSTRATI DI SILICIO PER CELLE FOTOVOLTAICHE DI NUOVA GENERAZIONE

A. Nottola, S. Tirelli, G. Prati (Istituto di Tecnologie della Comunicazione dell' Informazione e della Percezione (TeCIP), Scuola Superiore Sant'Anna, Pisa) L.V. Mercaldo, M. Izzi, P. Delli Veneri (ENEA)

Settembre 2016

## Report Ricerca di Sistema Elettrico

Accordo di Programma Ministero dello Sviluppo Economico - ENEA Piano Annuale di Realizzazione 2015

Area: Generazione di energia elettrica con basse emissioni di carbonio

Progetto: "Ricerca su Tecnologie Fotovoltaiche Innovative"

Obiettivo: Celle solari ad eterogiunzione a-Si/c-Si - Ottimizzazione del guadagno ottico in celle ad eterogiunzione di silicio: texturing del

silicio e sviluppo di TCO ad alta mobilità

silicio e sviluppo di TCO ad alta mobilita

Responsabile del Progetto: Paola Delli Veneri, ENEA

Il presente documento descrive le attività di ricerca svolte all'interno dell'Accordo di collaborazione "Nanostrutture su substrati di

Lucia Vittoria Mercaldo

Silicio per celle fotovoltaiche di nuova generazione"

Responsabile scientifico ENEA: Lucia V. Mercaldo

Responsabile scientifico Scuola Superiore Sant'Anna: Giancarlo Prati

## Indice

| SOMMA | .RIO                                                                                    | 4  |

|-------|-----------------------------------------------------------------------------------------|----|

| 1 IN7 | INTRODUZIONE                                                                            |    |

| 2 FAI | BBRICAZIONE DELLE METASUPERFICI                                                         | 6  |

| 2.1   | Îl processo di litografia                                                               | 6  |

| 2.2   | PROGETTAZIONE DEL PROCESSO DI ATTACCO AL PLASMA IN RELAZIONE AL PROFILO DELLE STRUTTURE | 13 |

| 2.3   | ATTACCO AL PLASMA DI DOT ARRAY                                                          | 16 |

| 2.4   | ATTACCO AL PLASMA DI PILLAR ARRAY                                                       | 18 |

| 3 CA  | RATTERIZZAZIONE DELLA QUALITÀ ELETTRONICA DEL WAFER NANOSTRUTTURATO                     | 19 |

| 4 CO  | NCLUSIONI                                                                               | 20 |

| 5 RIE | FRIMENTI BIRLIOGRAFICI                                                                  | 21 |

## Sommario

Questo documento descrive il lavoro di realizzazione di nanostrutture su substrati di silicio per celle fotovoltaiche di nuova generazione svolto nell'ambito dell'Accordo di collaborazione tra ENEA e Scuola Scuola Superiore Sant'Anna di Pisa. La strutturazione e la caratterizzazione morfologica sono state condotte presso il Centro Tecnologie per la Fotonica Integrata "INPHOTEC" della Scuola Superiore Sant'Anna, utilizzando le tecnologie disponibili per la fabbricazione di dispositivi fotonici integrati in silicio. ENEA ha fornito i progetti dei pattern da realizzare sul silicio e ha condotto i test di valutazione degli effetti del processo di strutturazione sulle proprietà elettroniche dei wafer. I pattern sono stati progettati dall'Università del Sannio in base a studi teorico/numerici nell'ambito di un Accordo di collaborazione parallelo tra ENEA e Unisannio (attività descritta nel Report RdS/PAR2015/294).

Sono state realizzate due diverse tipologie di pattern: matrice ortogonale di fori (dot array) e matrice di pillar cilindrici con due diversi diametri disposti in configurazione alternata. Date le caratteristiche geometriche delle strutture, con dimensioni critiche di poche centinaia o decine di nanometri, per la definizione del pattern si è dovuta impiegare la litografia a fascio elettronico. La realizzazione delle strutture ha comportato un lavoro di sviluppo di processi non standard per INPHOTEC, per risolvere alcune criticità poste dalle particolari geometrie da ottenere. Innanzitutto la risoluzione richiesta, soprattutto nel caso della matrice di pillar cilindrici, si avvicinava ai limiti caratteristici della litografia elettronica. Inoltre, il controllo dimensionale di strutture dalle dimensioni trasversali dell'ordine di 100 nm, con uno sviluppo di centinaia di nm in altezza, è particolarmente complesso. Un'ulteriore criticità è stata l'area di estensione del pattern ben più ampia rispetto alle applicazioni più frequenti in cui è utilizzata la litografia elettronica, che ha richiesto lo studio di soluzioni che permettessero di ottenere il miglior compromesso tra una risoluzione adeguata alla definizione delle strutture e tempi di processo compatibili con le risorse a disposizione. Infine, il controllo dell'inclinazione delle pareti dei dot ha richiesto strategie del processo di etching evolute, sviluppate specificamente per il progetto.

Il lavoro di messa a punto dei processi e i risultati ottenuti per le due tipologie di pattern sono riportati nella sezione 2, mentre la sezione 3 illustra la valutazione degli effetti del processo di strutturazione sulla qualità elettronica del wafer mediante misure di tempo di vita dei portatori di carica minoritari. Il rapporto è poi corredato da una introduzione che evidenza motivazioni e finalità del lavoro (sezione 1) e dalle conclusioni in sezione 4.

## 1 Introduzione

L'attività di ricerca qui descritta, formalizzata nell'ambito dell'Accordo di collaborazione tra ENEA e Scuola Superiore Sant'Anna di Pisa, si inquadra nella linea "Celle solari a eterogiunzione a-Si/c-Si su wafer di silicio p" del progetto "B.1.2 - Ricerca su tecnologie fotovoltaiche innovative" e in particolare nel subtask che mira allo sviluppo di opportune morfologie superficiali del wafer di silicio con l'obiettivo di ottimizzare il guadagno ottico nelle celle solari e quindi la corrente da esse ottenibile.

Tipicamente sulle superfici dei wafer di silicio vengono realizzate delle testurizzazioni piramidali random, attraverso attacchi chimici, per ridurre le perdite per riflessione della radiazione solare ed incrementare il cammino ottico nel dispositivo. L'efficacia della testurizzazione random è soddisfacente per wafer di spessore standard, ma per spessori tendenzialmente sempre più bassi, secondo il trend attuale dettato dall'abbattimento dei costi di produzione, è opportuno valutare degli approcci alternativi potenzialmente più efficienti nel sopperire all'incompleto assorbimento della luce. Oggetto della presente attività è appunto la realizzazione su wafer di silicio di texturing non convenzionali, progettati a questo scopo mediante studi teorico/numerici nell'ambito di un Accordo di Collaborazione parallelo tra ENEA e Università del Sannio. In particolare l'Università del Sannio si è dedicata allo studio e sviluppo di metasuperfici dielettriche (i dettagli dell'attività sono esposti nel report RdS/PAR2015/294). L'implementazione di texturing ispirati alle metasuperfici è un settore particolarmente interessante che rappresenta un cambiamento radicale rispetto agli schemi di light trapping convenzionali che fanno uso di reticoli di diffrazione e fenomeni di accoppiamento modale (fotonici o plasmonici). Di contro, la complessità realizzativa può rappresentare un limite pratico. La presente attività di ricerca esplorativa mira appunto ad evidenziare punti di forza e criticità dell'approccio.

Le attività dei due Accordi di Collaborazione (ENEA/Pisa ed ENEA/Unisannio) sono state condotte in parallelo. Durante la fase di progettazione delle opportune metasuperfici, il Centro Tecnologie per la Fotonica Integrata "INPHOTEC" della Scuola Superiore Sant'Anna di Pisa ha avviato il complesso lavoro di messa a punto dei vari passi di processo necessari per la nanostrutturazione del wafer, basandosi su un pattern preliminare caratterizzato da strutture con dimensioni geometriche dell'ordine di quelle ragionevolmente attese per i texturing ispirati alle metasuperfici. In particolare è stato scelto un pattern a matrice ortogonale di fori (dot array), da realizzare su un'area di 30x30 mm². L'area è stata definita in modo da essere compatibile con la strumentazione disponibile in ENEA per poi a valle valutare gli effetti del processo di strutturazione sulla qualità elettronica del wafer mediante misure di tempo di vita dei portatori di carica minoritari. Date le caratteristiche geometriche delle strutture, con dimensioni critiche di poche centinaia o decine di nanometri, per la definizione del pattern si è dovuta impiegare la litografia a fascio elettronico, poiché con la litografia ottica standard (in contatto o in prossimità), pur disponibile nei laboratori INPHOTEC, la migliore risoluzione ottenibile è di circa 1 micron. Inoltre, per il trasferimento del pattern al substrato di silicio, si è dovuto impiegare un processo di attacco al plasma (dry etching), perché i processi di attacco chimico in soluzione (wet etching) forniscono profili inclinati lungo i piani cristallini del silicio, non compatibili con le geometrie circolari richieste. Va evidenziato che la fabbricazione del pattern proposto ha comportato un lavoro di sviluppo di processi non standard per INPHOTEC, per risolvere varie criticità, tra cui la necessità di patternare aree ben più estese rispetto alle tipiche lavorazioni con litografia a fascio elettronico.

La prima e più corposa fase del lavoro ha avuto dunque il duplice scopo di sviluppare l'opportuno protocollo realizzativo e di valutare la compatibilità dei processi con l'uso successivo del wafer per l'applicazione fotovoltaica. Nella seconda fase si è passati alla realizzazione della metasuperficie progettata da Unisannio parallelamente alla prima fase del lavoro sperimentale. Il pattern in questo caso è costituito da una matrice di pillar cilindrici con due diversi diametri, disposti in configurazione alternata. Nel presente documento le lavorazioni delle due tipologie di pattern non sono presentate secondo la sequenza temporale, ma si è preferito un ordine logico dettato dagli step di processo. L'attività di fabbricazione delle nanostrutture e i risultati delle valutazioni morfologiche sono riportati nella sezione seguente. Nella

successiva sono invece riassunti i risultati delle misure di tempo di vita dei portatori di carica minoritari effettuate sui wafer strutturati e sottoposti a passivazione.

## 2 Fabbricazione delle metasuperfici

## 2.1 Il processo di litografia

La nanostrutturazione via litografia da fascio elettronico prevede vari passi di processo. Innanzitutto, il pattern definito su file viene trascritto sulla superficie da trattare rivestita con un film sensibile agli elettroni (resist). Con lo sviluppo in un appropriato solvente le strutture risultano dapprima impresse nel resist. Quest'ultimo funge a questo punto da maschera per trasferire il pattern nel substrato (nel nostro caso il wafer di silicio) mediante tecniche di etching. Questa sezione è dedicata allo step di litografia, ossia alla fase di definizione del pattern sul resist.

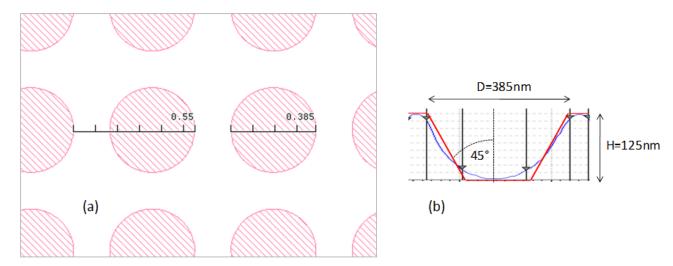

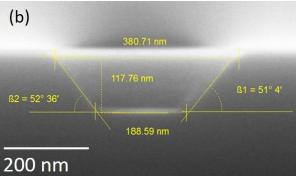

Come discusso nell'introduzione, si è lavorato su due diverse tipologie di pattern da riportare su wafer di silicio da 4 pollici. Il primo pattern realizzato è una matrice di fori (dot array) con diametro dei dot di 385 nm, passo del reticolo di 550 nm e profondità di scavo nel silicio di 125 nm, su un'area di (30x30) mm². In Figura 1(a) è riportato un dettaglio dello schema del pattern. Per quanto riguarda la forma del profilo dei dot, in attesa dei requisiti dallo studio teorico/numerico, è stata fissata un'inclinazione delle pareti di circa 45°, con i fori più stretti alla base (Figura 1(b)), quale caratteristica più conveniente in vista degli step successivi di realizzazione della cella solare sul wafer. Infatti, per completare poi il dispositivo, è prevista la deposizione di film semiconduttori ultrasottili, la cui qualità elettronica può essere inficiata da una morfologia di substrato con pareti troppo ripide. Questa condizione risulta dunque ideale per valutare gli effetti del complesso dei vari trattamenti del processo di nanostrutturazione sulla qualità elettronica ottenibile per il wafer di silicio ricoperto di film sottile passivante (sezione 3).

Figura 1. (a) Particolare del pattern impiegato per la fabbricazione della struttura in silicio (misure in μm). La parte tratteggiata rappresenta lo scavo nella superficie del silicio. (b) Schema del profilo da ottenere nei dot della nano-struttura (linea rossa).

Nella litografia a fascio elettronico [1], il resist viene esposto tramite una scansione del fascio con una determinata corrente e ad una determinata frequenza, su una griglia di punti con spaziatura dell'ordine dei nanometri. La dose di esposizione del resist, cioè la quantità di carica assorbita dal resist per unità di area, è legata agli altri parametri che caratterizzano l'esposizione dalla seguente relazione:

$$D = \frac{I}{f (BSS)^2} \tag{1}$$

dove I è la corrente del fascio elettronico che incide sul substrato, f è la frequenza di scansione e BSS (beam step size) è la spaziatura in x e y della griglia quadrata di punti sui quali avviene la scansione del fascio.

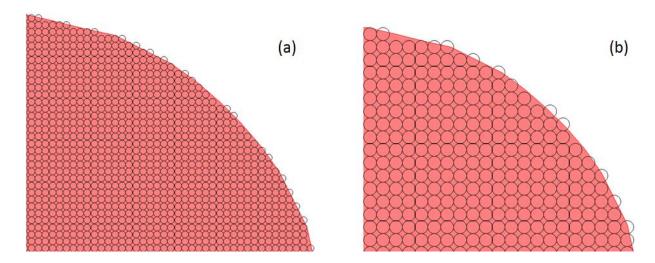

La tecnica tradizionale per ottenere la definizione delle geometrie in litografia elettronica consiste nel comporre il disegno eseguendo la scansione del fascio su una griglia di punti abbastanza vicini da approssimarne il profilo con una buona fedeltà. Ad esempio, in **Figura 2** viene mostrato schematicamente l'effetto di approssimazione del profilo curvo di un dot di 385 nm di diametro con una griglia di punti distanti 4 nm (**Figura 2(a)**) e con una griglia di punti distanti 8 nm (**Figura 2(b)**). Le dimensioni del diametro del fascio e della zona di interazione tra elettroni e resist contribuiscono ad un effetto medio di *smoothing* del contorno delle strutture, finché le griglia è abbastanza piccola rispetto alle dimensioni tipiche della zona di interazione.

Figura 2. Schematizzazione dell'effetto di approssimazione del profilo curvo di un dot di 385 nm di diametro con una griglia di punti distanti 4 nm (a) e con una griglia di punti distanti 8 nm (b).

Per geometrie curve di dimensioni sub- $\mu$ m è estremamente importante scegliere una spaziatura di griglia adeguata a fornire un contorno sufficientemente liscio: ciò impone valori di *BSS* di pochi nm. Un ruolo importante viene assunto anche dal rapporto tra *BSS* e diametro del fascio (proporzionale a sua volta alla corrente di probe): tale rapporto non può essere troppo grande, perché altrimenti non si riesce a ottenere una buona copertura del resist nella zona di esposizione, e si rischia di avere residui di resist sul substrato. La dose di esposizione del resist per la quale si ottengono strutture ben aperte e pulite è un parametro che dipende sostanzialmente dal tipo di resist e dal suo spessore: nel caso in esame, il resist a disposizione per la litografia e-beam, usato con spessori di circa 0.5  $\mu$ m, ha una dose ottimale di circa 300  $\mu$ C/cm². Inoltre, per quanto riguarda la frequenza di scansione del fascio elettronico, tale parametro dipende dal particolare sistema di litografia elettronica. La macchina disponibile presso i laboratori INPHOTEC (Vistec VB6-HR) può lavorare su un range di frequenze da 0.4 kHz a 25 MHz. Una volta fissati come discusso i valori di spaziatura di griglia, dose di esposizione e frequenza massima di scansione, la corrente di esposizione rimane determinata dall'equazione (1), e può assumere un valore massimo attorno ad 1nA.

Un primo test di esposizione elettronica del pattern richiesto è stato condotto utilizzando la metodologia convenzionale appena descritta, con un *BSS* di 4 nm, una dose di 300  $\mu$ C/cm² e una corrente di 0.7 nA. Nella **Tabella 1** si riportano i principali parametri di processo usati in questo caso.

Tabella 1. Parametri di processo per l'esposizione del dot array con metodologia convenzionale

#### Parametri e-beam

#### Parametri resist

| Tensione di accelerazione | 100 keV                | Tipo di resist        | AR-P6200   |

|---------------------------|------------------------|-----------------------|------------|

| Campo di deflessione      | 0.524288 mm            | Spessore resist       | 500 nm     |

| Corrente                  | 0.7 nA                 | Temperatura soft-bake | 150°C      |

| Beam Step Size            | 4 nm                   | Durata soft-bake      | 60 s       |

| Dose                      | 300 μC/cm <sup>2</sup> | Tipo di sviluppo      | AR 600-546 |

| Frequenza di scansione    | 14583 kHz              | Durata sviluppo       | 60 s       |

|                           |                        | Rinse                 | IPA        |

|                           |                        | Durata rinse          | 60 s       |

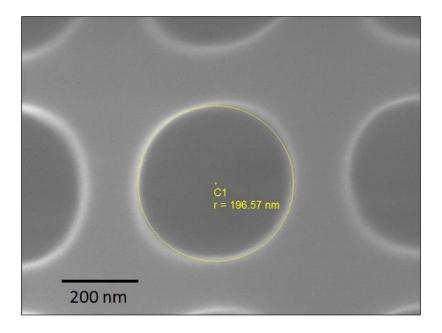

Nella **Figura 3** viene mostrata un'immagine al microscopio elettronico a scansione del risultato dell'esposizione. Si può notare che, a fronte del valore del diametro praticamente in specifica, il dot appare leggermente ovalizzato in direzione diagonale: ciò è da attribuirsi ad un astigmatismo del fascio del microscopio SEM non perfettamente corretto.

Figura 3. Immagine SEM del risultato dell'esposizione del dot array con la metodologia convenzionale, dopo sviluppo del resist. Il valore mostrato è il raggio medio della struttura non perfettamente circolare.

Come si evince da questo risultato, il metodo convenzionale di esposizione elettronica fornisce un pattern fedele al disegno, da utilizzare successivamente per il trasferimento al substrato. Purtroppo, il problema principale di questa tecnica è la durata del processo eccessivamente lunga: nel setup di litografia adoperato, per portare a termine l'esposizione di un dot array delle dimensioni richieste, sarebbe stato necessario un tempo pari ad oltre un mese. Poiché la durata del processo di litografia, a parità di area esposta, è approssimativamente pari al rapporto tra dose e corrente, in queste condizioni l'unico modo per velocizzare il processo e completarlo in tempi ragionevoli sarebbe quello di aumentare la corrente di ordini di grandezza, ma a spese della risoluzione, come abbiamo visto prima, e quindi della definizione del pattern.

Una tecnica alternativa che si può utilizzare nel caso di strutture circolari è quella di esporre ciascun dot con un singolo pixel, ossia con un singolo *beam-shot*, sfruttando la simmetria circolare del fascio di elettroni [2]. Per ottenere fori di diametro desiderato e controllato, e in particolare per aumentare il diametro rispetto ai pochi nm di un fascio ben focalizzato, si può agire in vari modi, innanzitutto modulando la corrente di

probe, poi ove possibile sfocando di proposito il fascio, e infine aumentando la dose di esposizione, il che equivale a ridurre la frequenza di scansione. Il sistema di litografia dei laboratori INPHOTEC non consente di modificare il fuoco del fascio in maniera controllata, quindi rimangono le altre due possibilità. In base a queste considerazioni, si è utilizzata la tecnica *single-shot*, scegliendo opportuni valori di corrente e di dose per ottenere una buona definizione del contorno dei dot e una durata del processo ragionevole, cioè al massimo di alcuni giorni. Bisogna notare che, nel caso di esposizione puntiforme, la formula (1) deve essere sostituita con la seguente:

$$D = \frac{I}{f} \tag{2}$$

dove i simboli assumono un significato identico a quelli dell'equazione (1). Bisogna precisare inoltre che relativamente al pattern in **Figura 1(a)**, per un'esposizione a *single-shot* è sufficiente usare un array di punti senza dimensioni disposti a distanze uguali al periodo. Per quanto riguarda la corrente di esposizione, sono stati eseguiti diversi test con vari valori. Per ragioni di sintesi, qui si riportano due casi. Nel primo si è usata una corrente relativamente alta, di 162 nA. Il risultato è mostrato in **Figura 4**. Come si nota, la forma dei dot è molto lontana da quella circolare, evidentemente a causa di una forte asimmetria del fascio elettronico rispetto al profilo circolare ideale. Il motivo non è stato individuato, ma un'ipotesi plausibile è che, a causa della corrente molto alta e quindi di un fascio relativamente largo, la propagazione lungo la colonna del sistema di litografia fosse perturbata da qualche elemento periferico interagente col bordo del fascio.

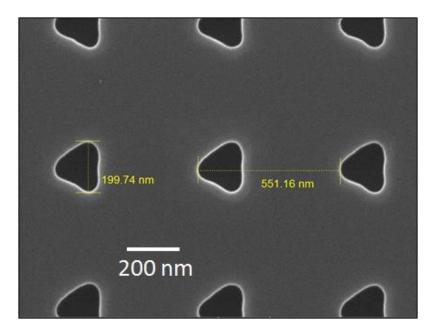

Figura 4. Immagine SEM del risultato dell'esposizione del dot array in modalità *single-shot*, ad una corrente di 162nA, dopo sviluppo del resist.

Per riprova, in un test successivo è stata usata una corrente ben più bassa, di 7 nA, quindi con uno *spot-size* di fascio inferiore, e si è ottenuto il risultato mostrato in **Figura 5**. In questo caso l'immagine SEM è stata presa dopo l'etching del silicio: i due profili che si distinguono sono quello alla base e quello alla sommità della struttura, e quest'ultimo ha un diametro di circa 360 nm (dose di esposizione leggermente inferiore a quella ottimale). Il contorno dei dot non è regolare come nel caso dell'esposizione in modalità convenzionale, tuttavia questo costituiva il miglior compromesso come già discusso. Questa rugosità del contorno non è stata spiegata, ma dall'osservazione che essa aumenta con la dose, si è ipotizzato che per la natura delle interazioni degli elettroni col resist e col substrato [3], al crescere del tempo di residenza del

Parametri e-beam

fascio, e quindi del numero di elettroni incidenti sullo stesso punto, aumentino anche le interazioni elastiche a lunga distanza, dove la distribuzione di energia assorbita dal resist ha un profilo più rumoroso.

Figura 5. Immagine SEM del risultato dell'esposizione del dot array in modalità *single-shot*, ad una corrente di 7nA, dopo etching del silicio. I valori mostrati corrispondono al raggio alla base e alla sommità delle strutture, e al passo della matrice.

Ad ogni modo, la corrente di 7 nA era troppo bassa per eseguire la litografia in pochi giorni, quindi si è cercato un valore ottimale che fornisse una buona qualità e un processo più efficiente. Il migliore compromesso è stato ottenuto con un valore della corrente di esposizione di 46 nA, e nella **Tabella 2** si riportano i principali parametri di processo usati in questo caso.

Tabella 2. Parametri di processo per l'esposizione del dot array con metodologia *single-shot*.

Parametri resist

|                           |             | r arametri resist     |            |

|---------------------------|-------------|-----------------------|------------|

| Tensione di accelerazione | 100 keV     | Tipo di resist        | AR-P6200   |

| Campo di deflessione      | 0.524288 mm | Spessore resist       | 500 nm     |

| Corrente                  | 46 nA       | Temperatura soft-bake | 150°C      |

| Beam Step Size            | -           | Durata soft-bake      | 60 s       |

| Dose                      | 200 mC      | Tipo di sviluppo      | AR 600-546 |

| Frequenza di scansione    | 364 kHz     | Durata sviluppo       | 60 s       |

|                           |             | Rinse                 | IPA        |

|                           |             | Durata rinse          | 60 s       |

|                           |             |                       |            |

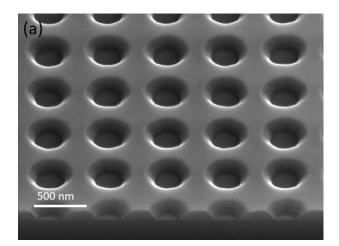

Il risultato finale (a valle dell'etching del silicio descritto in seguito) è mostrato nella **Figura 6**, in cui l'immagine è stata presa col campione inclinato e sono riportati i valori delle dimensioni dei dot alla base e alla sommità della struttura dove, con una dose ottimizzata, si sono ottenute le dimensioni in specifica. Il processo litografico per portare a termine l'esposizione del dot array su un'area di (30x30) mm², in questa configurazione ha richiesto 48 ore. I campioni di questa tipologia sono stati dedicati alle misure del tempo di vita dei portatori di carica minoritari effettuate in ENEA (Sezione 3).

Figura 6. Immagine SEM del risultato dell'esposizione del dot array in modalità *single-shot*, ad una corrente di 46nA, dopo etching del silicio. I valori mostrati corrispondono al raggio alla base e alla sommità delle strutture.

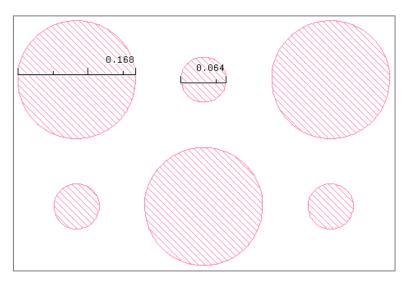

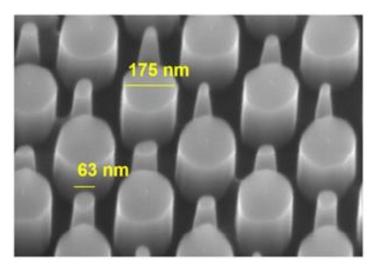

La seconda tipologia di pattern è una metasuperficie fornita da Unisannio tramite ENEA ed è una matrice di pillar cilindrici con due diversi diametri (64 e 168 nm) e un'altezza di 242 nm, disposti in una configurazione alternata come schematizzato nella **Figura 7**. La distanza tra i centri dei pillar in x e y è costante e pari a 181 nm. Contrariamente al caso del dot array, per i pillar è richiesto un profilo verticale, come derivato dallo studio numerico di Unisannio.

Figura 7. Particolare del pattern impiegato per strutturazione dello strato riflettore posteriore delle celle solari a film sottile (misure in μm). La parte tratteggiata rappresenta il silicio che deve rimanere in rilievo dopo l'attacco al plasma.

Dovendo usare il resist come maschera per il successivo dry etching, nell'esposizione della matrice di pillar con lo stesso resist impiegato per la matrice di dot, invece di esporre l'interno dei cerchi bisogna esporre tutta la zona circostante. In litografia c'è la possibilità di usare resist di tonalità differenti: quello descritto finora è un resist *positivo*, che nelle zone in cui è esposto agli elettroni viene rimosso durante lo sviluppo; l'opposto succede con un resist *negativo*, che viene rimosso dallo sviluppo nelle zone in cui non è stato

esposto. Per quanto discusso è chiaro che, in termini di durata del processo, per il dot array era particolarmente conveniente usare un resist positivo, mentre invece per la matrice di pillar la scelta migliore sarebbe un negativo, sia perché a parità di superficie totale, la percentuale di area da esporre sarebbe inferiore (per la precisione, il 39% dell'area totale anziché il 61%), sia soprattutto perché si potrebbe sfruttare il metodo di esposizione single-shot. Tuttavia, a partire dal periodo in cui è stato fornito il pattern da utilizzare per la matrice di pillar, i tempi di consegna di un nuovo resist negativo e lo sviluppo del relativo processo di litografia e attacco non avrebbero consentito la realizzazione di un prototipo nei tempi previsti dal progetto. Quindi sono state svolte attività preliminari usando lo stesso resist impiegato per il dot array.

Per quanto riguarda la tecnica di esposizione, si è usata la metodologia convenzionale descritta all'inizio del presente paragrafo. Date le diverse dimensioni dei pillar rispetto ai dot del caso precedente, soprattutto per i pillar più piccoli era necessario spingere la distanza tra i punti della griglia di scansione a valori ancora inferiori. Per la relazione (1) già discussa tra i parametri che caratterizzano l'esposizione, il *BSS* poteva assumere al minimo il valore di 2 nm, sufficiente ad avere una definizione accettabile delle strutture. Nei primi test di esposizione, si è usato il set di parametri riportato nella **Tabella 3**.

Tabella 3. Parametri di processo per l'esposizione del pillar array con metodologia convenzionale.

#### Parametri e-beam Parametri resist Tensione di accelerazione 100 keV AR-P6200 Tipo di resist 400 nm Campo di deflessione 0.524288 mm **Spessore resist** 150°C Corrente Temperatura soft-bake 0.1 nA **Beam Step Size** 2 nm **Durata soft-bake** 60 s Dose $170 \,\mu\text{C/cm}^2$ Tipo di sviluppo AR 600-546 Frequenza di scansione 14706 kHz Durata sviluppo 60 s **IPA** Rinse **Durata rinse** 60 s

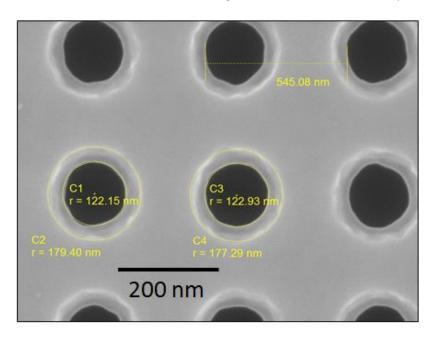

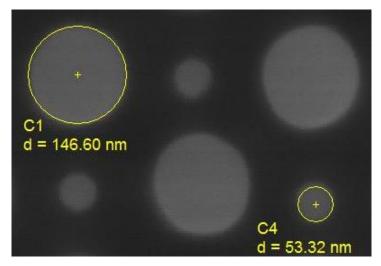

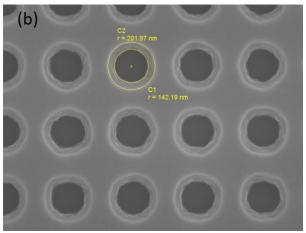

Nella **Figura 8** viene mostrata un'immagine al microscopio elettronico a scansione del risultato di uno di questi test. Si può notare che il diametro dei pillar è molto vicino a quello richiesto dal progetto, e comunque questo parametro va ottimizzato in funzione della dose di esposizione controllandone il valore dopo etching.

Figura 8. Immagine SEM del risultato dell'esposizione del pillar array, dopo sviluppo del resist. I valori mostrati corrispondono al diametro delle strutture.

## 2.2 Progettazione del processo di attacco al plasma in relazione al profilo delle strutture

Per il trasferimento del pattern al substrato di silicio, si è dovuto impiegare un processo di attacco al plasma (dry etching), perché i processi di attacco chimico in soluzione (wet etching) forniscono profili inclinati lungo i piani cristallini del silicio che non erano compatibili con le geometrie circolari richieste. Questa sezione fornisce una panoramica sulla progettazione del processo di etching in relazione al profilo desiderato per le strutture.

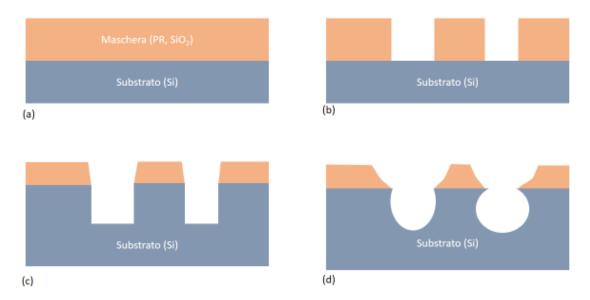

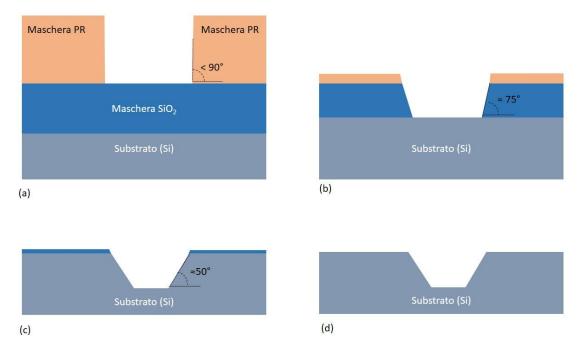

Figura 9. Schema di processo di dry etching con maschera di fotoresist (PR) oppure ossido di silicio (SiO<sub>2</sub>). Sezione del campione: (a) prima del processo di patterning; (b) dopo il patterning; (c) dopo un processo di dry etching anisotropo; (d) dopo un processo di etching isotropo.

La geometria da realizzare per la fabbricazione del pattern a pareti oblique (dot array) presenta criticità legate alle dimensioni molto ridotte del pattern e alla regolarità delle superfici e dei profili. Le dimensioni di 135 nm alla base del tronco di cono da realizzare (cfr. Figura 1(b)) possono mettere in evidenza una fenomenologia comune negli attacchi al plasma chiamata ARDE (Aspect Ratio Dependent Etching) [4]. Infatti, all'interno di strutture di dimensioni trasversali molto inferiori al micrometro o molto profonde, ovvero con aspetto di forma maggiore di 3:1, la dinamica del plasma procede in modo diverso rispetto alle aree aperte non strutturate. Questo fenomeno è in parte dovuto all'accumulo dei prodotti di reazione all'interno delle strutture di dimensioni ridotte e ad altri fenomeni locali che modificano le reazioni superficiali. I fenomeni di ARDE non possono essere eliminati, ma possono essere ridotti in modo da non interferire con la fabbricazione delle strutture. Tipicamente, processi che utilizzano alte energie di plasma, con flussi elevati di gas reagenti, risentono degli effetti ARDE in misura minore. Tuttavia, un processo con queste caratterische presenta solitamente delle velocità di etching elevate, che pongono difficoltà nel realizzare le ridotte profondità di attacco necessarie nei dispositivi in oggetto (125 nm, cfr. Figura 1(b)). Inoltre, processi di plasma a potenze elevate e con alti flussi di gas implicano spesso danni alla superficie delle strutture e un etching generalmente anisotropo.

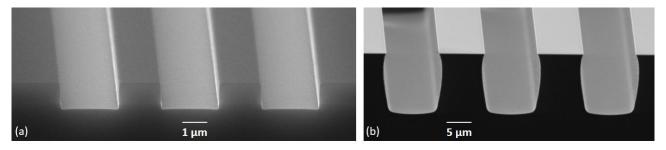

Figura 10. Fotografia al microscopio elettronico di sezioni di campioni dopo (a) etching anisotropo su SiO<sub>2</sub> e (b) etching isotropo su silicio.

Un confronto tra processi di etching isotropi e anisotropi è illustrato nella **Figura 9**. Le **Figura 9(a)** e **(b)** mostrano un campione pronto per l'attacco in plasma prima e dopo la definizione della maschera. La **Figura 9(c)** mostra l'effetto di un attacco al plasma fortemente anisotropo. Si noti che mentre il profilo della maschera dopo il patterning è di 90°, a causa di effetti termici e della non perfetta anisotropia dell'attacco, il profilo della maschera dopo il processo è leggermente inclinato. Infine, la **Figura 9(d)** mostra il risultato dopo un processo di plasma etching fortemente isotropo. È evidente che per ottenere la forma richiesta per gli obiettivi del presente progetto è necessario operare in un regime intermedio rispetto a quelli illustrati nei riquadri **(c)** e **(d)** della **Figura 9**. La **Figura 10** mostra le sezioni fotografate al microscopio elettronico di due campioni sottoposti ad attacco al plasma dopo un patterning delle maschera con semplici righe dritte. La sezione del campione dopo un etching di tipo anisotropo su SiO<sub>2</sub> è illustrato nella **Figura 10(a)** mentre la **Figura 10(b)** mostra un etching isotropo su silicio.

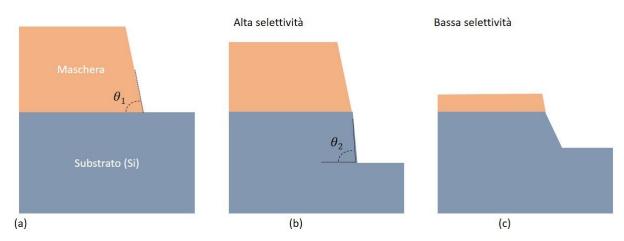

Un importante parametro che permette di realizzare pareti con pendenza definita è la selettività del processo di etching rispetto al materiale usato come maschera. Un'accurata calibrazione di questo parametro consente di ottenere pareti di pendenza ben definita. Partendo da una maschera di etching con pareti non perfettamente verticali (cfr. **Figura 9(c)**), è possibile modificare la pendenza tramite il processo di attacco. Il meccanismo che consente la regolazione della pendenza della parete dopo l'etching è illustrato in **Figura 11**. La **Figura 11(a)** mostra il campione e una maschera (per es., di fotoresist) non verticale. Si noti che la situazione iniziale dopo ogni processo litografico è quasi sempre quella riprodotta in figura. Infatti, il riscaldamento superficiale dovuto all'esposizione al plasma comporta sempre una minima deviazione dalla verticalità del profilo della maschera. La pendenza intrinseca della parete della maschera viene riprodotta in maniera ridotta nel caso di processo altamente selettivo, cfr. **Figura 11(b)**. Questo corrisponde alla situazione in cui la velocità di attacco della maschera è minore di quella del substrato. La pendenza della maschera verrà invece amplificata nel caso in cui il substrato venga attaccato più lentamente rispetto alla maschera, cfr. **Figura 11(c)**. Infatti, detto  $\gamma$  il rapporto tra le velocità di etching della maschera e del substrato, e detti  $\theta_1$  e  $\theta_2$  gli angoli formati dalle pareti della maschera e della struttura fabbricata, rispettivamente, da semplici calcoli trigonometrici si ottiene:

$$\theta_2 = \tan^{-1} \left( \frac{\tan \theta_1}{\gamma} \right)$$

Figura 11. Effetto di una differenza di selettività del processo di etching: (a) maschera e substrato preetching; (b) risultato dopo un processo ad alta selettività; (c) risultato dopo un processo a bassa selettività.

Figura 12. Sezione del substrato: (a) dopo la litografia elettronica e lo sviluppo del fotoresist; (b) substrato dopo il primo processo di etching; (c) dopo il secondo processo di etching; (d) dopo la rimozione della maschera rimasta.

In questo modo, utilizzando un processo anisotropo ma poco selettivo, è possibile in linea di principio ottenere l'angolo  $\theta_2$  desiderato. Si noti inoltre che l'angolo della maschera durante il processo di etching non rimane costante, in quanto effetti termici possono modificarne la forma. Questo accade specialmente nel caso di maschere di fotoresist, dato che questo materiale tende a diventare morbido e a contrarsi a temperature relativamente basse (100-130°C), facilmente raggiungibili sulla superficie di un campione sottoposto ad attacco al plasma.

La selettività di un attacco al plasma può essere però abbassata soltanto entro un certo limite. Quando la selettività diventa troppo bassa, infatti, i prodotti di reazione della maschera superano quantitativamente quelli del substrato: questo rende il processo poco controllabile o la superficie risultante troppo rugosa. Per

questo, al fine di ottenere la pendenza richiesta di 45°, si è deciso di procedere con un attacco al plasma in due successivi passaggi. Ciò consente di amplificare la pendenza nativa della maschera di fotoresist iterativamente tramite due passaggi con attacchi a bassa selettività. Il primo etching viene effettuato su SiO<sub>2</sub> con una maschera di resist. Questo passo trasferisce il pattern dal resist a una identica maschera di SiO<sub>2</sub> con pareti più pendenti rispetto a quelle del resist. La maschera di SiO<sub>2</sub> così definita viene poi usata per il secondo passaggio di etching su silicio. È stato dunque preparato il substrato di silicio ricoprendolo prima con 220 nm di SiO<sub>2</sub> tramite Plasma Enhanced Chemical Vapor Deposition (PECVD) con silano (SiH<sub>4</sub>) e protossido di azoto (N₂O) come precursori. In seguito, il substrato così preparato è stato ricoperto da ebeam resist e patternato tramite il processo descritto nella Sezione 2.1. La sezione del substrato dopo il patterning e-beam è schematizzata in Figura 12(a). Gli spessori del fotoresist e della maschera di SiO<sub>2</sub> sono pari a 500 e 220 nm, rispettivamente. La maschera di fotoresist possiede una pendenza iniziale minore di 90°, difficilmente definibile con precisione a causa della deformazione subita sotto il fascio elettronico del microscopio elettronico durante l'ispezione e anche sotto l'effetto del plasma durante il processo. Assumendo dunque una pendenza iniziale effettiva di 85°, che tiene conto di eventuali effetti termici durante l'attacco al plasma, dopo un primo processo di etching con selettività y = 0.35, si otterrebbe una pendenza di circa 75° (**Figura 12(b)**). Dopo un secondo processo di etching, con una selettività pari a  $\gamma$  = 0.28 (Figura 12(c)), si otterrebbe la pendenza desiderata di 45°. La maschera rimanente di SiO<sub>2</sub> è infine rimossa tramite immersione del substrato in una soluzione a base di acido fosforico (Figura 12(d)).

## 2.3 Attacco al plasma di dot array

Un'intensa attività è stata dedicata allo sviluppo di processi di etching più adatti a realizzare le caratteristiche definite nella progettazione del processo descritta nella Sezione 2.2. Il processo di plasma etching è stato attuato in una macchina per l'attacco al plasma Omega 201 di Trikon/SPTS. Il reattore al plasma contiene due sorgenti a radiofrequenza (RF) che ionizzano i gas formando il plasma. La prima è una sorgente assiale, la cui potenza viene definita potenza di bias, in quando concorre maggiormente all'instaurarsi di una differenza di potenziale tra il substrato e il voltaggio di riferimento. La seconda sorgente RF, chiamata M=0 Reactive Ionization (MORI), realizza nel plasma un'onda elicoidale, che aumenta la concentrazione di radicali senza necessariamente modificare la differenza di potenziale del campione. La combinazione di queste due potenze consente la massima libertà nella definizione del processo di etching.

Per il primo processo di attacco è stata sviluppata una chimica di etching basata su trifluorometano (CHF3) e ossigeno  $(O_2)$ . I radicali provenienti dalla scissione del trifluorometano sono particolarmente attivi nella rimozione del  $SiO_2$ , che in questo caso rappresenta il substrato da attaccare. I radicali dell'ossigeno attaccano invece tutti i composti organici, come quelli che compongono il fotoresist, che in questo caso costituisce la maschera. I due gas si mescolano durante l'attacco e, tramite la regolazione del rapporto tra i due, è possibile determinare la selettività del processo di etching, ovvero la velocità di attacco della maschera rispetto a quella del substrato. Tuttavia, poiché i radicali dell'ossigeno inibiscono anche le reazioni tra  $CHF_3$  e  $SIO_2$ , aumentando troppo la concentrazione di ossigeno nella mistura, la velocità di attacco di  $SiO_2$  diminuisce rapidamente. Ciò pone un limite inferiore alla selettività che è possibile raggiungere. Le caratteristiche del processo di etching utilizzato per il primo passo sono illustrate in **Tabella 4.** La selettività del primo passo di etching è pari a circa  $\gamma = 0.46$ .

Tabella 4. Composizione e caratteristiche dei processi di etching utilizzati.

| Etching step 1          |          | Etching step 2         |         |

|-------------------------|----------|------------------------|---------|

| Flusso CHF <sub>3</sub> | 100 sccm | Flusso SF <sub>6</sub> |         |

| Flusso O <sub>2</sub>   | 15 sccm  | Flusso O <sub>2</sub>  |         |

| Potenza bias            | 50 W     | Potenza bias           | 170 W   |

| Potenza MORI            | 400 W    | Potenza MORI           | 0 W     |

| Pressione               | 20 mTorr | Pressione              | 2 mTorr |

| Temperatura             | -15 C    | Temperatura            | -15 C   |

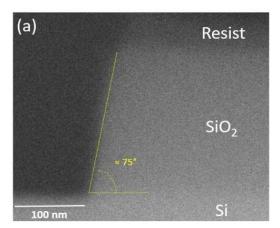

Figura 13. Risultati di test di etching su campione di prova (a) dopo il primo step di attacco; (b) dopo il secondo step.

Figura 14. Foto da microscopio elettronico della sezione di due prototipi di strutture finali. La struttura (a) presenta un diametro maggiore pari a 500 nm.

Durante lo sviluppo del processo i due step sono stati applicati a campioni di prova che sono stati poi sezionati tramite cleaving e ispezionati al microscopio elettronico.

La **Figura 13(a)** mostra una sezione di un campione dopo il primo processo di attacco. Lo spessore di resist residuo è circa 30 nm, rispetto a uno spessore inziale di 500 nm. La profondità di attacco nel  $SiO_2$  è di 220 nm, con una pendenza di circa 75°, affetta da una certa incertezza di misura dovuta dalla risoluzione del microscopio elettronico.

Il secondo passo di attacco è stato eseguito con una chimica standard per l'attacco in plasma su substrati di silicio, consistente in una mistura di esafluoruro di zolfo ( $SF_6$ ) e ossigeno. I dettagli del processo di attacco finale sono forniti nella **Tabella 4**. La **Figura 13(b)** mostra la sezione di un campione dopo una versione non finale del secondo processo di attacco. Nel processo di sviluppo applicato al campione di **Figura 13(b)**, la potenza di bias era 60 W, mentre gli altri parametri erano come quelli riportati in **Tabella 4**. Lo spessore di  $SiO_2$  residuo è circa 20 nm, rispetto a uno spessore inziale di 220 nm, la profondità di attacco nel Si è di 120 nm, con una pendenza di circa 66° nella parte più superficiale dell'attacco e 52° in quella più profonda. La dinamica dell'attacco cambia dunque al variare della profondità. A questo effetto si è ovviato aumentando la potenza di bias da 60 a 170 W, definendo il processo finale con i parametri riportati in **Tabella 4**. Questa modifica ha portato a ottenere un profilo lineare anche dopo il secondo attacco.

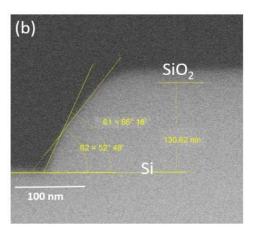

La Figura 14 mostra due test su strutture morfologicamente molto vicine a quelle finali, alle quali è stato applicato il processo ottimizzato con i parametri descritti in Tabella 4. La Figura 14(a) mostra la sezione centrale di una apertura circolare avente diametro maggiore di circa 500 nm, ovvero più grande delle specifiche richieste. La Figura 14(b) mostra invece una struttura avente un diametro prossimo alle specifiche. Si noti che l'angolo della parete dipende dalle dimensioni dell'apertura, a causa degli effetti ARDE. Si è dunque verificato che il processo finale produce delle strutturi compatibili con le specifiche. Il processo è dunque stato applicato, con i parametri identici al campione di test mostrato in Figura 14(b), a un pattern litografato su un'area ampia. Questo pattern è poi stato sezionato e ispezionato prima della fabbricazione del campione finale.

La **Figura 15(a)** riporta una fotografia al microscopio elettronico di un test su ampia area con geometria e processo ottimizzati e analoghi al campioni finale. La vista inclinata permette di ispezionare la sezione e verificare la regolarità del pattern accentuandone la tridimensionalità. Infine, una fotografia SEM dall'alto del campione finale è riportata in **Figura 15(b)**.

Figura 15. (a) fotografia al microscopio elettronico della sezione di un test pattern analogo al campione finale, il campione è inclinato per esaltare la tridimensionalità delle strutture; (b) vista dall'alto del campione finale.

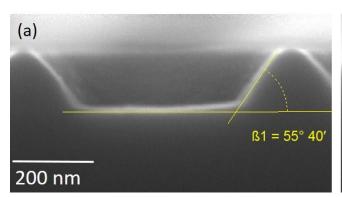

## 2.4 Attacco al plasma di pillar array

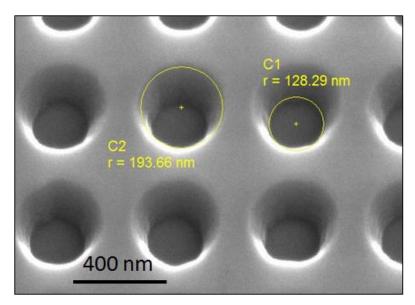

La realizzazione della struttura illustrata nella Figura 7 richiede caratteristiche di attacco al plasma molto diverse rispetto a quelle usate per il dot array. Per ottenere delle pareti verticali, è infatti necessario utilizzare un processo estremamente anisotropo e selettivo rispetto alla maschera di resist utilizzata per realizzare il pattern. Il processo di attacco impiega una chimica composta di esafluoruro di zolfo e di trifluorometano, con una bassa potenza RF. Date le limitate profondità richieste (240 nm) la velocità di attacco deve essere bassa. D'altra parte, processi molto lenti possono portare a una isotropia del profilo, in contrasto con le caratteristiche necessarie per la matrice di pillar. I parametri del processo al plasma utilizzato sono illustrati nella Tabella 5. Una fotografia SEM di un campione di silicio al quale è stato applicato il processo al plasma è mostrata in Figura 16. Benché le dimensioni dei pillar siano prossime alla specifica, si nota una pendenza non desiderata sul profilo delle strutture. Il processo al plasma utilizzato, benché presenti un'elevata anisotropia, possiede una selettività tra silicio e resist non elevata, pari a circa 1:1. Come spiegato nella Sezione 2.2, una bassa selettività del processo porta a un'amplificazione della pendenza nella maschera. Un processo più selettivo potrebbe migliorare il profilo e consentire l'utilizzo di un resist più sottile. Una soluzione alternativa è quella di adottare un approccio in due step, analogamente a quello adottato per la matrice di dot illustrato nella Sezione 2.2. In tal modo si potrebbe sfruttare l'elevata selettività di attacco del silicio rispetto a una maschera sottile di SiO<sub>2</sub>, che sarebbe strutturata tramite uno strato di resist sottile. Questo approccio può essere perseguito, preferibilmente con l'utilizzo di

un resist negativo. Il risultato riportato in **Figura 16** dimostra che le strutture richieste dal progetto possono essere realizzate con le tecnologie e i processi disponibili presso INPHOTEC; tuttavia, per una fabbricazione con un controllo accurato delle dimensioni e della verticalità dei profili su grandi aree (~1 cm²), necessaria per l'integrazione nelle celle solari, occorrerebbero ulteriori sviluppi del processo e l'uso di diversi materiali non attualmente a disposizione.

Tabella 5. Composizione del processo al plasma per la realizzazione dei pillar.

Flusso CHF<sub>3</sub> 20 sccm

Flusso SF<sub>6</sub> 45 sccm

Potenza bias 50 W

Potenza MORI 0 W

Pressione 1.5 mTorr

Temperatura 5°C

Figura 16. Fotografia SEM di un campione a matrice di pillar dopo il processo di etching.

## 3 Caratterizzazione della qualità elettronica del wafer nanostrutturato

I wafer di silicio nanostrutturati secondo il dot array, per i quali è stato possibile fabbricare il pattern su larga area (30x30 mm²), sono stati sottoposti in ENEA a un indagine volta a verificare la compatibilità dei processi usati, descritti nella sezione precedente, per l'applicazione del wafer quale strato assorbitore di una cella solare ad eterogiunzione. Per tali tipi di dispositivi la qualità delle superfici del wafer, che si interfacciano poi con successivi strati semiconduttori ultrasottili, è fondamentale per garantire buone prestazioni elettriche della cella solare.

Anche per un wafer non patternato (o con pattern piramidale random standard) la superficie rappresenta un problema a causa della rottura della simmetria del reticolo cristallino che comporta la presenza di dangling bonds, legami di silicio "appesi". Tali legami insaturi fungono da centri di ricombinazione per le cariche fotogenerate e questo si traduce in un abbassamento della tensione di circuito aperto  $(V_{oc})$  della cella solare e quindi dell'efficienza di conversione. Questo problema viene fortemente mitigato con la deposizione di uno strato ultrasottile di semiconduttore, tipicamente il silicio amorfo (a-Si:H) o sue leghe più trasparenti come l'ossido di silicio (a-SiO<sub>x</sub>:H), che passiva (o satura) i dangling bonds, riducendo

drasticamente la concentrazione dei centri di ricombinazione. La qualità di passivazione di tale strato è legata a vari fattori strutturali e chimici del film il cui controllo dipende a sua volta dai parametri del processo di deposizione. Essa è valutata mediante misura del tempo di vita medio dei portatori minoritari (τ) nel wafer di Si sulle cui superfici è stato depositato il film (misura effettuata mediante la tecnica di photoconductance decay utilizzando un Sinton lifetime tester). Gli strati "passivanti" di a-Si:H o di a-SiO<sub>x</sub>:H sono fabbricati nei laboratori ENEA mediante tecnologia Plasma Enhanced Chemical Vapour Deposition (PECVD). Nel presente test sono stati utilizzati strati di a-SiO<sub>x</sub>:H recentemente ottimizzati, cresciuti da miscele gassose di silano, idrogeno e biossido di carbonio e sottoposti a trattamenti termici a 300°C in atmosfera di azoto.

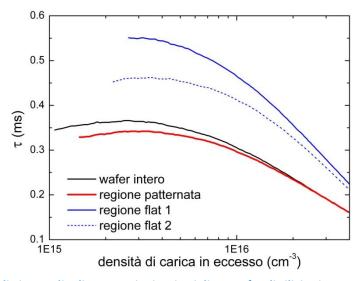

In **Figura 17** è riportato l'andamento misurato per il tempo di vita al variare dell'iniezione (densità di carica in eccesso a seguito dell'illuminazione) per un wafer nanostrutturato e passivato. La valutazione sull'intero wafer mostra valori di  $\tau$  (a livello di iniezione di  $4x10^{15}$  cm<sup>-3</sup>) di 0.36 ms. Sezionando il wafer, in modo da isolare la regione patternata di area  $30 \times 30$  mm<sup>2</sup>, è stato possibile valutare separatamente il tempo di vita relativo al wafer flat (regioni laterali) e al wafer nanostrutturato (regione centrale). Le regioni flat mostrano valori tra 0.45 e 0.55 ms, compatibili con i tipici valori ottenuti con i film di a-SiO<sub>x</sub>:H utilizzati, con delle variazioni tra le varie zone legate a una possibile disuniformità di spessore del film passivante sulla larga area. La regione patternata centrale presenta invece un  $\tau$  di 0.34 ms, praticamente confrontabile al valore misurato sull'intero wafer, che mostra come il tempo di vita dei portatori valutato sull'intero wafer sia dominato dalla regione a più alta ricombinazione. In ogni caso la riduzione di  $\tau$  rispetto alle regioni flat resta limitata (intorno a 20-40%). Tale risultato dimostra che il possibile danneggiamento della superficie del wafer dai processi di *etching* al plasma si mantiene entro limiti accettabili.

Figura 17. Tempo di vita medio di portatori minoritari di un wafer di silicio tipo p nanostrutturato con pattern a matrice di fori e passivato.

### 4 Conclusioni

La presente attività è stata focalizzata sulla realizzazione su wafer di silicio di texturing non convenzionali ispirati alle metasuperfici, con l'obiettivo di ottimizzare il guadagno ottico nelle celle solari ad eterogiunzione in silicio cristallino, e quindi la corrente da esse ottenibile, soprattutto nella prospettiva di utilizzo di wafer sempre più sottili. Nello specifico, presso la Scuola Sant'Anna di Pisa sono state realizzate due diverse tipologie di pattern: matrice ortogonale di fori a tronco di cono, o dot array, e matrice di pillar cilindrici con due diversi diametri disposti in configurazione alternata (pattern progettato da Unisannio). Il

dot array con le specifiche richieste è stato realizzato con successo, utilizzando una tecnica di litografia single-shot e un'hard mask di ossido di silicio per il successivo attacco al plasma. Per quanto riguarda la più complessa fabbricazione della matrice di pillar, il pattern è stato realizzato, per il momento su piccola area, con dimensioni che differiscono per meno del 10% dalle specifiche richieste. Ciò ha consentito di dimostrare che la metasuperficie progettata da Unisannio può essere realizzata con le tecnologie e i processi disponibili presso INPHOTEC; tuttavia, per una fabbricazione con un controllo accurato delle dimensioni e della verticalità dei profili su grandi aree (~1 cm²), necessaria per l'applicazione fotovoltaica almeno su scala dimostrativa, occorrono ulteriori sviluppi del processo ricorrendo anche all'uso di materiali differenti di cui non è stato possibile rifornirsi nei tempi di progetto. I campioni con strutturazione tipo dot array su larga area (30x30 mm²) sono stati dedicati alla valutazione di possibili danni alla qualità elettronica del wafer. La caratterizzazione, portata avanti in ENEA, ha mostrato valori accettabili del tempo di vita medio dei portatori di carica minoritari a valle della passivazione. Si può concludere che le procedure di nanopatterning messe a punto sono compatibili con l'utilizzo dei wafer per l'applicazione fotovoltaica.

## 5 Riferimenti bibliografici

- [1] S. Cabrini, S. Kawata (Eds.), "Electron Beam Lithography", in Nanofabrication handbook (2012), 9-40, CRC Press, Boca Raton, FL, USA.

- [2] T. Stomeo, A. Passaseo, R. Cingolani, M. De Vittorio, "Fast nanopatterning of two-dimensional photonic crystals by electron beam lithography", Superlattices and Microstructures **36** (2004), 265–270.

- [3] J. Zhou, X. Yang, "Monte Carlo simulation of process parameters in electron beam lithography for thick resist patterning", J. Vac. Sci. Technol. B **24** (2006), 1202-1209.

- [4] I. W. Rangelow, "Critical tasks in high aspect ratio silicon dry etching for microelectromechanical systems", J. Vac. Sci. Technol. A **21**, (2003), 1550-1562.

## Curriculum scientifico del gruppo di lavoro della Scuola Superiore Sant'Anna di Pisa

Alessandro Nottola graduated from University of Roma "La Sapienza" in Physics, in 1997. He mainly worked in private companies as a lithography process engineer in the development and prototyping of Optical Integrated Circuits (Pirelli Labs) and as a laser process engineer in the production of Silicon Thin Film Photovoltaic Modules (Pramac Solar). He also worked as an R&D engineer in the field of III-V Concentrating Photovoltaics (RSE). He is currently in charge of the lithography processes in the Integrated Photonic Technology Center (INPHOTEC) within the Scuola Superiore Sant'Anna in Pisa (Italy).

**Stefano Tirelli** was born in Reggio Emilia, Italy. He received his M.S. degree in physics from the University of Pisa, Italy, in 2008. In 2014 he got his PhD in Electrical Engineering at the Swiss Federal Institute of Technology (ETH) conducting research on gallium nitride high power transistors. From 2015 he works as Process Engineer at the InPhoTec center of the Sant'Anna School in Pisa. His research interests include material science, electronic and optical device physics, micro- and nano-fabrication technologies.

Giancarlo Prati was born in Rome in 1946. He graduated in 1972 at Pisa University in electronic engineering "cum laude", alumnus of Scuola Superiore Sant'Anna. In 1978-79 he was Visiting Scientist at USC (University of Southern California), working in optical communications with Robert M.Gagliardi , renowned scientist. His activity has developed since then: in 1982 he was Visiting Associate Professor at University of Massachusetts at Amherst, until 1986 he was Researcher with the CNR Center for Radio Transmission in Pisa, since 1986 he was professor of telecommunications at Genoa University in Italy, then since 1988 at Parma University in Italy. In 1992-98 he was Dean of Engineering at Parma University. In 1993-95 he was member of the CNR Feasibility Committee for "Photonics" project. In 1997-99 he was a member of the Scientific Committee of the Italian Space Agency. From 1995 to 2004 he was Director of CNIT, a Consortium of 37 Universities for Telecommunications he promoted. In 2000 moved to Scuola Superiore Sant'Anna in Pisa to create a new research center on Photonic Networks, which counts today (2016) around 100 researchers. From 2002 to 2004 he was Director of the Research Division and Vice Director of the same School.

Since 1999 he is a member of the TPC of ECOC. In 2004 he was elected to the IEEE Fellow grade. Since 10 June 2013 he was appointed as Member in the ERC Starting Grants evaluation for the panel PE7 - Systems and Communication Engineering. Currently he is member of the CNIT Managing Committee.

Professor Prati pioneered the area of free space optical communications for deep space applications in the late Seventies and early Eighties at the University of Southern California. Since then prof Prati has promoted and managed several national/international projects on optical communications and co/authored more than 70 papers and 5 patents. He has also worked in the Seventies on Digital Radio Links, becoming co-recipient of the "W.Bennett" Prize Paper Award for his work on blind equalization of fading radio channels.