RICERCA DI SISTEMA ELETTRICO

Studio e analisi di sistemi di controllo implementabili con logiche programmabili per il miglioramento delle prestazioni e della sicurezza di impianti nucleari di nuova concezione

S. Di Gennaro, B.Castillo–Toledo, F. Memmi

STUDIO E ANALISI DI SISTEMI DI CONTROLLO IMPLEMENTABILI CON LOGICHE PROGRAMMABILI PER IL MIGLIORAMENTO DELLE PRESTAZIONI E DELLA SICUREZZA DI IMPIANTI NUCLEARI DI NUOVA CONCEZIONE Stefano Di Gennaro, Bernardino,Castillo–Toledo, Fabrizio Memmi Università dell'Aquila Settembre 2012

Report Ricerca di Sistema Elettrico

Accordo di Programma Ministero dello Sviluppo Economico - ENEA

Area: Governo, Gestione e Sviluppo, del Sistema Elettrico Nazionale

Progetto: Nuovo Nucleare da Fissione: Collaborazioni Internazionali e sviluppo Competenze in Materia Nucleare

Responsabile del Progetto: Massimo Sepielli, ENEA

# CENTER OF EXCELLENCE DEWS Department of Electrical and Information Engineering

University of L'Aquila, V. G. Gronchi 18, 67100, L'Aquila, Italy

Deliverable 1

Study and analysis of control systems implementable by programmable logic for performance and safety improvements of novel nuclear plants

Studio ed analisi di sistemi di controllo implementabili con logiche programmabili per il miglioramento della prestazioni e della sicurezza di impianti nucleari di nuova concezione

Authors: Stefano DI GENNARO, Bernardino CASTILLO–TOLEDO, Fabrizio MEMMI Principal Investigator: Prof. Stefano DI GENNARO

Project PAR 2011 June 30, 2012

#### Abstract

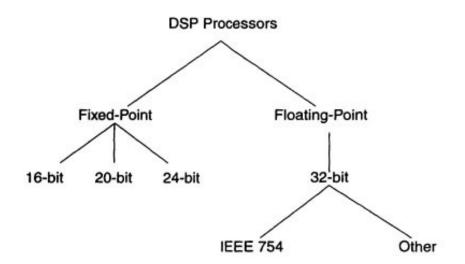

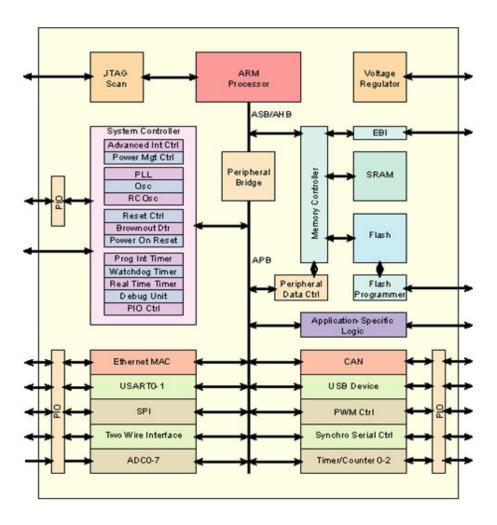

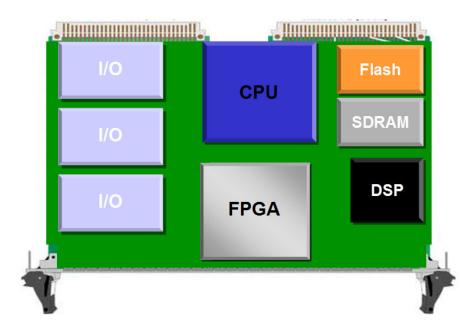

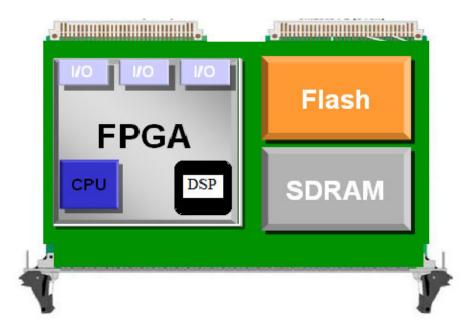

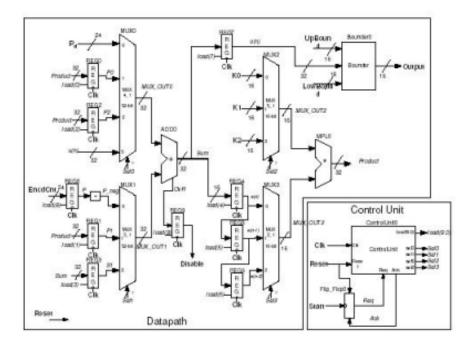

In this deliverable, the aspects concerning the digital implementation of a control law on a physical device are analyzed, from the viewpoint of the study, design and realization of supervisory, control and protection systems for improving the performance and safety of novel nuclear plants. In fact, it is well known that the implementation of control laws with zero order holders, commonly used, introduce a delay and hence could bring to unstable behaviors. A technique called self-triggered control allows determining the sampling times necessary to implement the controller, preserving the desired performance. In the digital logic system scenario, there are many architectures suitable for realizing different kinds of control algorithms, considering performances in terms of timing, power consumption and resources availability. Different implementation solutions are hence studied, from microprocessors to custom devices for digital processing, in order to obtain an evaluation about benefits and drawbacks. In particular, FPGA technology will be studied in detail, explaining how designers can exploit their potentialities in applications of parallel computation, control and digital signal processing.

#### Riassunto

In questo documento vengono analizzati gli aspetti relativi all'implementazione digitale di una legge di controllo su un dispositivo fisico, dal punto di vista dello studio, progetto e realizzazione di sistemi di supervisione, controllo e protezione per aumentare la prestazione e sicurezza di impianti nucleari di nuova concezione. Infatti è ben noto che l'implementazione di leggi di controllo mediante organi di tenuta di ordine zero, comunemente utilizzati, introducono un ritardo e quindi possono portare a comportamenti instabili. Una tecnica chiamata controllo auto-innescante permette di determinare i tempi di campionamento successivi per implementare il controllore, preservando le prestazioni desiderate. Nello scenario dei sistemi a logica digitale, vi sono molte architetture adatte a realizzare diversi tipi di algoritmi di controllo, considerando prestazioni in termini di tempi, consumo di potenza e disponibilità di risorse. Varie soluzioni implementative sono quindi studiate, dai microprocessori a dispositivi personalizzabili, per ottenere una valutazione dei benefici e dei svantaggi. In particolare la tecnologia FPGA sarà studiata in dettaglio, spiegando come i progettisti possono sfruttare i loro potenziali in applicazioni di calcolo parallelo, controllo e processamento del segnale digitale.

## 1 The Nonlinear Continuous Time Controllers Implemented by Digital Devices

In [1], [2], the supervision, control and protection systems for nuclear reactors of new generation has been analyzed. Using a mathematical model of the primary circuit, simple enough for the control purposes but accurate enough to capture the nonlinear, time–varying, switching nature of the plant, a dynamic level controller is determined for the pressurizer water level. Moreover, two dynamics controllers have been designed for the pressurizer pressure. These controllers may not use measurements of the pressurizer pressure, relying only on the pressurizer wall temperature measurements.

The aforementioned controllers are continuous time, namely the assume that the state variables, necessary to implement the feedback, are continuously measured, while the control is computed at each time instant and applied to the controlled system. In reality, such controllers are implemented by digital devices, much more flexible than analog devices. Other notable characteristics are the multitasking capability of the digital controllers, and the possibility of parallel data acquisition and computation. This last property allows faster computation times, so approaching the performance of the digitally implemented controller to that obtainable with an analogically implemented controller.

### 1.1 Digital Implementation of Control Strategies: Some Important Issues to Take into Account

A very popular way of determining and implementing a controller on a digital device is to design the controller assuming the continuous time behavior of the system, and then implement the continuous controller by means of zero order holders, commonly used for digital implementations. Such controller are usually named "emulated" controllers. It easy to understand that this design technique could bring to unsatisfactory behaviors of the controlled system if the sampling time is high. In fact, it is well known that the effect of the presence of zero order holders is equivalent to a delay of approximatively the half of the sampling time. As well known also in the case of linear systems, a delay could bring to unstable behaviors.

The effects of the sampling and zero order holders can be seen also in a alternative way. Let us

suppose that the controller is determined considering the continuous time dynamics

$$\dot{x} = f(x, u)$$

where  $x \in \mathcal{D}_x$  represent the vector of the state variables,  $u \in \mathcal{D}_u$  is the vector of the input variables,  $\in \mathcal{D}_x \subset \mathbb{R}^n$ ,  $\in \mathcal{D}_u \subset \mathbb{R}^p$  are the domains where x, u take values, and  $f : \mathcal{D}_x \times \mathcal{D}_u \to \mathbb{R}^n$  is the function describing the system dynamics. Usually, this function is requested to fulfill suitable conditions to ensure existence and unicity of the solution for each initial state  $x(0) = x_0$ , such as the (local) Lipschitz condition, namely

$$||f(x_1, u) - f(x_2, u)|| \le L||x_1 - x_2||$$

with  $x_1, x_2 \in \mathcal{D}_x$  two generic state values, and *L* a constant (in the local version of this property, *L* depends on the region  $\Omega$  considered) called Lipschitz constant. The value of *L* measures how much *f* varies when  $x_2$  differs from  $x_1$ , and is a measure of the "nonlinearity" of *f*. Considering that *L* can be determined considering the maximum value the jacobian norm  $||\partial f/\partial x||$  takes on the region  $\Omega$  that is taken into account, it is clear that *L* measures the "derivative" of *f*.

Let us assume that a controller  $u = \alpha(x)$  has been determined somehow. This is a continuous time control, and should be better denoted as  $u_t = \alpha(x_t)$ , where *t* is the continuous time. For the sake of simplicity, the dependence on *t* is usually dropped. This controller is normally implemented considering the sampled state value  $x_k$  at time  $t = k\delta$ , and the (constant) numerical value  $u_k = \alpha(x_k)$  is applied to the system by means of zero holder devices, that hold the value  $u_k$  over the time interval  $[k\delta, (k+1)\delta)$ , where  $\delta$  is the sampling time and  $k \in \mathbb{Z}$  is an integer.

It is therefore clear that eventually the dynamics of the controlled system is given by

$$\dot{x} = f(x, \alpha(x_k))$$

which apparently differ from the ones

$$\dot{x} = f(x, \alpha(x))$$

obtained when the continuous time controller is applied. It is clear that the effect of the sampling is equivalent to a disturbance d acting on the system, since

$$\dot{x} = f(x, \alpha(x_k)) = f(x, \alpha(x)) + d$$

where

$$d = f(x, \alpha(x_k)) - f(x, \alpha(x)).$$

This disturbance is periodically zero at the sampling time  $t = k\delta$ , while grows when  $t > k\delta$ . The growth of this disturbance depends on the "nonlinearity" of *f* and, obviously, on the value of  $\delta$ . In particular,

when  $\delta$  is small the disturbance remains small enough to affect greatly the performance of the controller. But in the case in which  $\delta$  could take (relatively) big values, *d* can take bigger values. The measure of how big this disturbance value can be is given, again, by the Lipschitz constant *L*, since

$$||d|| = ||f(x, \alpha(x_k)) - f(x, \alpha(x))|| \le L||x - x_k|| \le L \max_{x \in \Omega} ||x - x_k|| = d_{\max}$$

The effect of this disturbance on the closed loop behavior is to take away x from the desired value. Let x us assume<sup>1</sup> that one desires that x goes asymptotically to x = 0, by means of the control  $u = \alpha(x)$ . This control can be designed<sup>2</sup> making use of a (positive definite) Lyapunov function V such that, when d = 0

$$\dot{V} = \frac{\partial V}{\partial x} f(x, \alpha(x))$$

is definite negative. If  $\alpha_3(||x||)$  is a  $\mathcal{K}$  function<sup>3</sup> this can be expressed saying that

$$\dot{V} = \frac{\partial V}{\partial x} f(x, \alpha(x)) \le -\alpha_3(||x||).$$

This means that V, which can take the meaning of a (generalized) energy function, is decreasing as time passes. Therefore, asymptotically x tends to the origin. When d is nonzero, namely when the emulated controller is used, what can be ensured<sup>4</sup> is that  $\dot{V}$  is negative definite outside a region

$$\dot{V} = \frac{\partial V}{\partial x} f(x, \alpha(x_k)) = \frac{\partial V}{\partial x} \Big[ f(x, \alpha(x)) + d \Big] \le -\alpha_3(||x||) + \alpha_4(||x||) d_{\max}(x_k) + \alpha_4(||x||) d_{\max}(x_k) \Big]$$

where

$$\left\|\frac{\partial V}{\partial x}\right\| \le \alpha_4(\|x\|)$$

and  $\alpha_4(||x||)$  is an appropriate  $\mathcal{K}$  function<sup>5</sup>. To determine such a region, a ball of the origin of radius  $\mu$ , one has to "spend" a part of the term  $-\alpha_3(||x||)$  (ensuring the asymptotic convergence of x to the origin) to "counteract" the positive term  $\alpha_4(||x||)d_{\text{max}}$

$$\dot{V} \le -(1-\vartheta)\alpha_3(||x||) + \alpha_4(||x||)d_{\max} - \vartheta\alpha_3(||x||) \le -(1-\vartheta)\alpha_3(||x||)$$

for

$$||x|| \ge \mu := \alpha_3^{-1} \left( \frac{1}{\vartheta} \max_{x \in \Omega} \alpha_4(||x||) d_{\max} \right)$$

where  $\vartheta \in (0, 1)$ . As a result of the fact that  $\dot{V}$  is negative definite outside the ball of radius  $\mu$ , the trajectories of the controlled system tend asymptotically to the ball of radius  $\mu$  and remains in there. This

<sup>&</sup>lt;sup>1</sup>It is possible to show that the origin can be considered as equilibrium point, after an appropriate change of coordinate.

<sup>&</sup>lt;sup>2</sup>The controllers designed in [1] have been obtained precisely with a Lyapunov–based technique.

<sup>&</sup>lt;sup>3</sup>A K function  $\alpha_3(r)$  is a continuous function such that  $\alpha_3(0) = 0$ , and is strictly increasing, see [8].

<sup>&</sup>lt;sup>4</sup>A "worst–case scenario is here considered.

<sup>&</sup>lt;sup>5</sup>It is possible to show that such a function  $\alpha_4(||x||)$  does exists.

property is usually called "practical stability" of the origin, since generalizes the property of asymptotic stability to the origin. It is also called "ultimate boundedness" of the trajectories, since the solution  $x_t$  of the differential equation will enter, at a certain time instant, the ball of radius  $\mu$  and will remain in it. The choice of  $\vartheta$  determines a trade–off between of the dimension of the region about the origin and the convergence velocity of the state trajectories to this ball.

Other aspects can be also be addressed<sup>6</sup>. Notably, the fact that the sampling of the state variables necessary to the control implies that the control law is applied with a time delay  $\delta$ , so that the system dynamics are more precisely given by

$$\dot{x} = f(x, u_{k-1}).$$

The resolution of this problem, that can be addressed by means of predictors of the form

$$\dot{\xi} = f(\xi, \alpha(\xi_k))$$

$$u_k = \alpha(\xi_k)$$

goes far beyond the scope of the deliverable. In any case, also this effect can be seen as a disturbance acting on the system, since the system dynamics can be written as

$$\dot{x} = f(x, \alpha(x_{k-1})) = f(x, \alpha(x)) + \bar{d}$$

with

$$\bar{d} = d + f(x, \alpha(x_{k-1})) - f(x, \alpha(x_k))$$

and treated in a similar way.

From the previous discussion, it is clear that the effect due to the sampling can be seen as due, mainly, to a persistent perturbation acting on the system. It is also clear that the effect of this disturbance is smaller if smaller is the amplitude of the disturbance which, in turn, diminishes as the sampling time  $\delta$  is smaller. The aim of the present deliverable is to study criteria ensuring better implementations of control laws and logics on digital programmable devices, with the goal of improving the performance and safety in nuclear plants of novel conception. In particular, more effective digital platform will be studied, which render the implementation of control law more flexible and effective.

#### 1.2 A Mathematical Model of the Primary Circuit of a PWR

In [1] a mathematical model of the primary circuit of a PWR has been considered. The reader can find in [1] the details of this model, given by<sup>7</sup>

<sup>&</sup>lt;sup>6</sup>Further effects, such as quantizations effects, are not considered here, since considered negligible.

<sup>&</sup>lt;sup>7</sup>The subindices "r", "pc", "sg", "pr" refer to the reactor, primary circuit, steam generator, and pressurizer, respectively.

$$\begin{split} \dot{N} &= -\frac{p_{0} + p_{1}v + p_{2}v^{2}}{\Lambda}N + S \\ \dot{M}_{pc} &= m_{in} - m_{out} \\ \dot{T}_{pc} &= \frac{1}{c_{p,pc}M_{pc}} \Big[ c_{p,pc}m_{in}(T_{pc,i} - T_{pc}) + c_{p,pc}m_{out}\varDelta + c_{\psi}N - n_{sg}k_{t,sg}(T_{pc} - T_{sg}) - W_{loss,pc} \Big] \\ \dot{T}_{sg} &= \frac{1}{c_{p,sg}^{l}M_{sg}} \Big[ c_{p,sg}^{l}m_{sg}T_{sg,sw} - c_{p,sg}^{v}m_{sg}T_{sg} - m_{sg}E_{evap,sg} + k_{t,sg}(T_{pc} - T_{sg}) - W_{loss,sg} \Big] \\ \dot{T}_{pr} &= \frac{1}{c_{p,pr}M_{pr}} \Big[ -k_{wall}(T_{pr} - T_{pr,wall}) + W_{heat,pr} + \delta_{pr} \Big( c_{p,pc}m_{pr}(T_{pc} + \varDelta) - c_{p,pr}m_{pr}T_{pr} \Big) \Big] \\ \dot{T}_{pr,wall} &= \frac{1}{c_{p,wall}} \Big[ k_{wall}(T_{pr} - T_{pr,wall}) - W_{loss,pr} \Big] \end{split}$$

where the state variables are the neutron flux N (in %), the overall mass in the primary circuit  $M_{pc}$  (in kg), the average temperature of the water in the primary circuit  $T_{pc}$  (in °C), the average secondary circuit liquid temperature  $T_{sg}$  (in °C), the pressurizer water/wall temperature  $T_{pr}$ ,  $T_{pr,wall}$  (in °C), and where

$$\begin{split} M_{pr} &= M_{pc} - \varphi(T_{pc}) V_{pc,0}, \qquad \varphi(T_{pc}) = c_{\varphi,0} + c_{\varphi,1} T_{pc} - c_{\varphi,2} T_{pc}^2 \\ m_{pr} &= m_{in} - m_{out} - \frac{1}{c_{p,pc} M_{pc}} \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} V_{pc,0} \Big[ c_{p,pc} m_{in} (T_{pc,i} - T_{pc}) + c_{p,pc} m_{out} \varDelta \\ &+ c_{\psi} N - n_{sg} k_{t,sg} (T_{pc} - T_{sg}) - W_{loss,pc} \Big]. \end{split}$$

In (1) v,  $m_{in}$ ,  $W_{heat,pr}$  are the input variables, while  $T_{pc,i}$ ,  $m_{out}$ ,  $m_{sg}$ ,  $M_{sg}$ ,  $T_{sg,sw}$  can be considered as disturbances. The model (1) is hybrid and nonlinear, since the equation of  $T_{pr}$  contains the switching term  $\delta_{pr}$ , which is 1 if  $m_{pr} > 0$  and 0 if  $m_{pr} \le 0$ . Moreover, it is simple enough for the control purposes but accurate enough to capture the nonlinear, time–varying, switching nature of the plant.

The (measurable) outputs of the systems are the reactor power  $W_r(N)$ , the steam generator pressure  $p_{sg}$  (in kPa), the pressurizer pressure  $p_{pr}$  (in kPa), the pressurizer water level  $l_{pr}$  (in m)

$$W_{r}(N) = c_{\psi}N$$

$$p_{sg} = p_{*,T}(T_{sg}) = c_{0} - c_{1}T_{sg} + c_{2}T_{sg}^{2}$$

$$p_{pr} = p_{*,T}(T_{pr}) = c_{0} - c_{1}T_{pr} + c_{2}T_{pr}^{2}$$

$$l_{pr}(M_{pc}, T_{pc}) = \frac{1}{A_{pr}} \left(\frac{M_{pc}}{\varphi(T_{pc})} - V_{pc,0}\right).$$

(2)

The model parameters are reported in Table 1.

#### 1.3 The Pressurizer Inventory and Pressure Controllers

The controller for pressurizer water level and pressure determined in [1] are dynamic controller relying only on the pressurizer wall temperature measurements. Considering a reference level  $l_{pr,ref}$ , usually

| Reactor                                               |                                                                              |                        |                       |

|-------------------------------------------------------|------------------------------------------------------------------------------|------------------------|-----------------------|

| Neutron flux (state variable)                         | N                                                                            | 00.2                   | %                     |

| × /                                                   | N                                                                            | 99.3<br>0              |                       |

| Control rod position (input)                          | V                                                                            | -                      | cm                    |

| Reactor power (output)                                | W <sub>r</sub>                                                               | $13.654 \times 10^{8}$ | W                     |

| Constant in the reactor power equation                | $c_{\psi}$                                                                   | $13.75 \times 10^{6}$  | W/%                   |

| Generation time                                       | Λ                                                                            | 10 <sup>-5</sup>       | S                     |

| Rod reactivity coefficients                           | $p_0$                                                                        | $2.85 \times 10^{-4}$  | m                     |

|                                                       | $p_1$                                                                        | $6.08 \times 10^{-5}$  | m <sup>-1</sup>       |

|                                                       | $p_2$                                                                        | $1.322 \times 10^{-4}$ | m <sup>-2</sup>       |

| Flux of the constant neutron source                   | $S^{P_2}$                                                                    | 2830.5                 | %/s                   |

| Total fraction of delayed neutrons                    | β                                                                            | 0.0064                 | 10/5                  |

| 2                                                     |                                                                              |                        | s <sup>-1</sup>       |

| Average half-life                                     | λ                                                                            | 0.1                    | S -                   |

| Primary circuit                                       |                                                                              |                        |                       |

| Overall mass in the primary circuit (state)           | $M_{pc}$                                                                     | $2 \times 10^{5}$      | kg                    |

| Water average temperature (state)                     | $T_{pc}$                                                                     | 281.13                 | °C                    |

| Inlet mass flow rate (input)                          | min                                                                          | 1.4222                 | kg/s                  |

| Outlet mass flow rate (disturbance)                   | mout                                                                         | 2.11                   | kg/s                  |

| Hot leg water temperature                             | $T_{pc,hl}$                                                                  | 296.13                 | °Č                    |

| Cold leg water temperature                            | $T_{pc,cl}$                                                                  | 266.13                 | °C                    |

| Inlet temperature (disturbance)                       | $T_{pc,i}$                                                                   | 258.85                 | °Č                    |

| Specific heat at 282°C                                | $c_{p,pc}$                                                                   | 5355                   | J/kg/K                |

| Heat transfer coefficient                             |                                                                              | $9.5296 \times 10^{6}$ | W/K                   |

|                                                       | $k_{t,sg}$                                                                   |                        |                       |

| Heat loss                                             | $W_{loss,pc}$                                                                | $2.996 \times 10^{7}$  | W                     |

| Water nominal volume                                  | $V_{pc,0}$                                                                   | 242                    | m <sup>3</sup>        |

| Water nominal mass                                    | $M_{pc,0}$                                                                   | $2 \times 10^{5}$      | kg                    |

| Differences $T_{pc,hl} - T_{pc} = T_{pc} - T_{pc,cl}$ | Δ                                                                            | 15                     | °C                    |

| Pressurizer                                           |                                                                              |                        |                       |

| Water temperature (state)                             | T <sub>pr</sub>                                                              | 326.57                 | °C                    |

| Heating power (input)                                 | W <sub>heat,pr</sub>                                                         | 168                    | kW                    |

| Water level (output)                                  | l <sub>pr</sub>                                                              | 4.8                    | m                     |

| Pressure (output)                                     | $p_{pr}$                                                                     | $123 \times 10^{2}$    | kPa                   |

| Water specific heat at 325°                           |                                                                              | 6873.1                 | J/kg/K                |

|                                                       | c <sub>p,pr</sub>                                                            | $6.4516 \times 10^7$   | J/°C                  |

| Heat capacity of the wall                             | $c_{p,wall}$                                                                 |                        |                       |

| Wall heat transfer coefficient                        | k <sub>wall</sub>                                                            | $1.9267 \times 10^{8}$ | W/°C                  |

| Heat loss                                             | W <sub>loss,pr</sub>                                                         | $1.6823 \times 10^5$   | W                     |

| Water mass                                            | M <sub>pr</sub>                                                              | 19400                  | kg                    |

| Vessel cross section                                  | $A_{pr}$                                                                     | 4.52                   | m <sup>2</sup>        |

| Vessel volume                                         | V <sub>pr,vessel</sub>                                                       | 44                     | m <sup>3</sup>        |

| Steam generator                                       |                                                                              |                        |                       |

| Average secondary circuit liquid temperature (state)  | $T_{sg}$                                                                     | 257.78                 | °C                    |

| Secondary circ. water specific heat at 260°           | cl                                                                           | 3809.9                 | J/kg/K                |

| Secondary circ. valuer specific heat at 260°          | $\left \begin{array}{c}T_{sg}\\c_{p,sg}^{l}\\c_{p,sg}^{v}\end{array}\right $ | 3635.6                 | J/kg/K                |

| Heat loss                                             | $W_{loss,sg}$                                                                | $1.8932 \times 10^7$   | W                     |

|                                                       |                                                                              | $1.658 \times 10^{6}$  |                       |

| Evaporation energy at 260°                            | $E_{\text{evap},sg}$                                                         |                        | J/kg                  |

| Water mass                                            | $M_{sg}$                                                                     | 34920                  | kg                    |

| Water level                                           | l <sub>sg</sub>                                                              | 1.850                  | m                     |

| Steam pressure (output)                               | $p_{sg}$                                                                     | $45.3 \times 10^2$     | kPa                   |

| Secondary water mass flow rate (disturbance)          | m <sub>sg</sub>                                                              | 119.31                 | kg/s                  |

| Secondary circ. steam mass flow rate                  | m <sub>sg,ss</sub>                                                           | 119.31                 | kg/s                  |

| Secondary circ. water mass flow rate                  | $m_{sg,sw}$                                                                  | 119.31                 | kg/s                  |

| Secondary circ. inlet temperature (disturbance)       | $T_{sg,sw}$                                                                  | 220.85                 | °Č                    |

| Number of steam generators                            | $n_{sg}$                                                                     | 6                      |                       |

| Power transferred to the steam generators             | $n_{sg}W_{sg}$                                                               | $13.351 \times 10^{8}$ | W                     |

| Functions                                             | -38 38                                                                       |                        |                       |

| Saturated vapor pressure                              | $p_{*,T}(T)$                                                                 |                        | kPa                   |

| Coefficients for quadratic approximation              |                                                                              | 20001 70               | kPa                   |

| Coefficients for quadratic approximation              |                                                                              | 28884.78               |                       |

|                                                       | <i>c</i> <sub>1</sub>                                                        | 258.01                 | kPa/°C                |

|                                                       | <i>c</i> <sub>2</sub>                                                        | 0.63455                | kPa/°C <sup>2</sup>   |

| Water density                                         | $\varphi(T)$                                                                 |                        | kg/m <sup>3</sup>     |

| Coefficients for quadratic approximation              | $c_{\varphi,0}$                                                              | 581.2                  | kg/m <sup>3</sup>     |

|                                                       | $c_{\varphi,1}$                                                              | 2.98                   | kg/m <sup>3</sup> /°C |

|                                                       | $c_{\varphi,2}^{\varphi,i}$                                                  | 0.00848                | $kg/m^3/^{\circ}C^2$  |

| L                                                     | ψ,                                                                           |                        | 0, , -                |

proportional to a mean value between the cold and the hot leg temperatures, with a drift to give a proper value [16]

$$l_{pr,ref} = c_{r,1}(T_{pc,cl} + T_{pc,hl}) - c_{r,2} = 2c_{r,1}T_{pc} - c_{r,2}$$

the inventory control for the pressurizer water level  $l_{pr}$  is given by

$$\begin{split} \dot{I}_{e_{lpr}} &= l_{pr} - l_{pr,\text{ref}} \\ m_{in} &= \frac{A_{pr}}{\psi(M_{pc}, T_{pc})} \bigg[ - \left( k_p (l_{pr} - l_{pr,\text{ref}}) + k_i I_{e_{lpr}} \right) \varphi^2(T_{pc}) + m_{out}^\circ \varphi(T_{pc}) \\ &+ \frac{1}{c_{p,pc}} \bigg( \frac{2c_{r,1}}{M_{pc}} \varphi^2(T_{pc}) + \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} \bigg) \bigg( c_{p,pc} m_{out}^\circ \Delta^\circ + c_{\psi} N - n_{sg} k_{t,sg} (T_{pc} - T_{sg}) - W_{loss,pc}^\circ \bigg) \bigg] \end{split}$$

(3)

with  $k_p, k_i > 0$ ,

$$\begin{split} \psi(M_{pc},T_{pc}) &= \varphi(T_{pc}) - (T_{pc,i}^{\circ} - T_{pc}) \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} - \frac{2c_{r,1}A_{pr}}{M_{pc}} (T_{pc,i}^{\circ} - T_{pc})\varphi^2(T_{pc}) \\ \varphi(T_{pc}) &= c_{\varphi,0} + c_{\varphi,1}T_{pc} - c_{\varphi,2}T_{pc}^2 \\ \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} &= c_{\varphi,1} - 2c_{\varphi,2}T_{pc}. \end{split}$$

Due to the the nominal disturbance values  $\Delta^{\circ}$ ,  $T_{pc,i}^{\circ}$ ,  $m_{out}^{\circ}$ ,  $W_{loss,pc}^{\circ}$ , and to their variations  $\delta_{\Delta} = \Delta - \Delta^{\circ}$ ,  $\delta_{T_{pc,i}} = T_{pc,i} - T_{pc,i}^{\circ}$ ,  $\delta_{m_{out}} = m_{out} - m_{out}^{\circ}$ ,  $\delta_{W_{loss,pc}} = W_{loss,pc} - W_{loss,pc}^{\circ}$ , this controller ensures practical exponential stability of the error level, i.e.  $e_{l_{pr}}$ ,  $\dot{e}_{l_{pr}}$  tend to a neighborhood of the origin of radius

$$\mu = \frac{\kappa}{\vartheta \lambda_{\min}^{Q}} ||P|| \delta_{\max}$$

where  $\kappa = \max_t ||\Psi||$ ,

$$\Psi = \frac{1}{\varphi^2(T_{pc})} \frac{1}{A_{pr}} \begin{pmatrix} 0 & 0 & 0 & 0 \\ -\frac{\partial \varphi(T_{pc})}{\partial T_{pc}} m_{in} & -\varphi(T_{pc}) - \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} \varDelta^\circ & -\frac{\partial \varphi(T_{pc})}{\partial T_{pc}} m_{out}^\circ & \frac{1}{c_{p,pc}} \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} & -\frac{\partial \varphi(T_{pc})}{\partial T_{pc}} \end{pmatrix}.$$

and  $\vartheta \in (0, 1)$ , *P* is solution of  $PA + A^T P = -2Q$  for a fixed  $Q = Q^T > 0$ ,  $\lambda_{\min}^Q$  is the minimum eigenvalue of Q,

$$A = \begin{pmatrix} 0 & 1 \\ -k_i & -k_p \end{pmatrix}$$

and  $\delta_{\text{max}}$  is the maximum variation with respect to the nominal disturbance values.

As far as the pressurizer pressure controller is concerned, a first nonlinear dynamic controller can be designed transforming the pressurizer pressure reference  $p_{pr,ref}$  into a pressurizer water reference temperature  $T_{pr,ref}$ , inverting the relation obtained from (2)

$$p_{pr,\text{ref}} = c_0 - c_1 T_{pr,\text{ref}} + c_2 T_{pr,\text{ref}}^2$$

that can be uniquely inverted about the operating point of pressurizer temperature

$$T_{pr,ref} = \frac{c_1 + \sqrt{c_1^2 - 4c_2(c_0 - p_{pr,ref})}}{2c_2}$$

$$\dot{T}_{pr,ref} = \frac{2\dot{p}_{pr,ref}}{\sqrt{c_1^2 - 4c_2(c_0 - p_{pr,ref})}}.$$

The dynamic controller, which depends on the (measured) temperature  $T_{pr,wall}$ , but not on the (unmeasured) temperature  $T_{pr}$

$$W_{heat,pr,ref} = c_{p,pr} M_{pr} \Big[ \dot{T}_{pr,ref} + \frac{k_{wall}}{c_{p,pr} M_{pr}} (T_{pr,ref} - T_{pr,wall,ref}) - \delta_{pr} \Big( \frac{c_{p,pc} m_{pr}^{\circ}}{c_{p,pr} M_{pr}} (T_{pc} + \varDelta^{\circ}) - \frac{m_{pr}^{\circ}}{M_{pr}} T_{pr,ref} \Big) \Big]$$

$$(4)$$

$$W_{heat,pr} = u_{e,W} + W_{heat,pr,ref}$$

$$\dot{\hat{T}}_{pr} = -\left(\frac{m_{pr}^{\circ}}{M_{pr}} + \frac{k_{wall}}{c_{p,pr}M_{pr}}\right)\hat{T}_{pr} + \frac{k_{wall}}{c_{p,pr}M_{pr}}T_{pr,wall} + \frac{1}{c_{p,pr}M_{pr}}W_{heat,pr} + \frac{c_{p,pc}m_{pr}^{\circ}}{c_{p,pr}M_{pr}}(T_{pc} + \Delta^{\circ})$$

$$\dot{T}_{pr,wall,ref} = \frac{k_{wall}}{c_{p,wall}}T_{pr,ref} - \frac{k_{wall}}{c_{p,wall}}T_{pr,wall,ref} + k_{i}I_{e_{T_{pr,wall}}} - \frac{1}{c_{p,wall}}W_{loss,pr}^{\circ}$$

$$\dot{I}_{e_{T_{pr,wall}}} = T_{pr,wall} - T_{pr,wall,ref} \qquad (5)$$

$$W_{heat,pr} = -k_{wall}(T_{pr,wall} - T_{pr,wall,ref}) - \frac{c_{p,pr}}{c_{p,wall}}k_{wall}M_{pr}B^{T}P\left(\frac{I_{e_{T_{pr,wall}}}}{T_{pr,wall,ref}}\right)$$

$$c_{p,pr}M_{pr}\left[\dot{T}_{pr,ref} + \frac{k_{wall}}{c_{p,pr}M_{pr}}(T_{pr,ref} - T_{pr,wall,ref}) - \delta_{pr}\left(\frac{c_{p,pc}m_{pr}^{\circ}}{c_{p,pr}M_{pr}}(T_{pc} + \Delta^{\circ}) - \frac{m_{pr}^{\circ}}{M_{pr}}T_{pr,ref}\right)\right]$$

ensures the practical exponential stability of the error temperatures, with  $k_i > 0$ ,  $k_p = \frac{k_{wall}}{c_{p,wall}} > 0$ ,  $T_{pr,wall,ref}(0) = T_{pr,ref}(0) - W_{loss,pr}^{\circ}/k_{wall}$ ,  $M_{pr} = M_{pc} - \varphi(T_{pc})V_{pc,0}$ ,

$$m_{pr}^{\circ} = m_{in} - m_{out}^{\circ} - \frac{1}{c_{p,pc}M_{pc}} \frac{\partial\varphi(T_{pc})}{\partial T_{pc}} V_{pc,0} \Big[ c_{p,pc}m_{in}(T_{pc,i}^{\circ} - T_{pc}) + c_{p,pc}m_{out}^{\circ} \mathcal{A}^{\circ} + c_{\psi}N - n_{sg}k_{t,sg}(T_{pc} - T_{sg}) - W_{loss,pc}^{\circ} \Big]$$

and  $P = P^T > 0$  solution of the Lyapunov equation

$$PA + A^T P = -2Q, \qquad A = \begin{pmatrix} 0 & 1 \\ -k_i & -\frac{k_{wall}}{c_{p,wall}} \end{pmatrix}$$

for a fixed  $Q = Q^T > 0$ , and  $B = (0 \ 1)^T$ .

An alternative (dynamic switching nonlinear) controller for the pressurizer pressure is given by

$$\begin{split} \dot{I}_{e_{ppr}} &= c_0 - c_1 \hat{T}_{pr} + c_2 \hat{T}_{pr}^2 - p_{pr,ref} \\ \dot{\xi} &= \hat{T}_{pr} - T_{pr,wall} - \frac{1}{k_{wall}} W_{loss,pr}^\circ - \frac{1}{k} \frac{1}{c_{p,pr} M_{pr}} C_{pr} \\ \hat{T}_{pr} &= \kappa \Big( \frac{c_{p,wall}}{k_{wall}} T_{pr,wall} - \xi \Big) \\ C_{pr} &= \frac{c_{p,pr} M_{pr}}{-c_1 + 2c_2 \hat{T}_{pr}} \Big( \dot{p}_{pr,ref} - K_p \Big( c_0 - c_1 \hat{T}_{pr} + c_2 \hat{T}_{pr}^2 - p_{pr,ref} \Big) - K_i I_{e_{ppr}} \Big) \\ W_{heat,pr} &= k_{wall} (\hat{T}_{pr} - T_{pr,wall}) + C_{pr} + \delta_{pr} \Big( c_{p,pr} m_{pr}^\circ \hat{T}_{pr} - c_{p,pc} m_{pr}^\circ (T_{pc} + \Delta^\circ) \Big) \end{split}$$

(6)

where  $\kappa$ ,  $K_p$ ,  $K_i > 0$ ,  $I_{e_{ppr}}(0) = 0$ ,  $\xi(0) = -\hat{T}_{pr}(0)/k + c_{p,wall}T_{pr,wall}(0)/k_{wall}$  and, as already defined,  $\delta_{pr}$  is 1 if  $m_{pr} > 0$  and 0 otherwise.

#### 1.4 Digital Implementation of the Control Laws

We have already noted that the implementation of control laws by means of digital devices determines a disturbances acting on the feedback system. In this section we consider a further aspect, the digital implementation of derivatives. In fact, in (3), (5), (6) the derivative  $\dot{I}_{e_{lpr}}$ ,  $\dot{T}_{pr}$ ,  $\dot{T}_{pr,wall,ref}$ ,  $\dot{I}_{e_{T_{pr,wall}}}$ ,  $\dot{I}_{e_{ppr}}$ ,  $\dot{\xi}$ have to be implemented numerically. Let us consider a feedback system with  $u = \alpha(x)$  a certain control law applied to control the system  $\dot{x} = \bar{f}(x, u)$ . The closed–loop dynamics is hence

$$\dot{x} = \bar{f}(x, \alpha(x)) := f(x)$$

A simple method to approximate by a digital computer the real time solution of this differential equation is to consider the Euler's rule, relying on the definition of derivative

$$\dot{x} = \lim_{\varDelta t \to 0} \frac{\varDelta x}{\varDelta t}.$$

Here  $\Delta x$  is the change in x over the time interval  $\Delta t$ . Even if  $\Delta t$  does not tends to zero, the previous relation is approximately true

$$\dot{x}|_{t_k} \simeq \frac{x_{k+1} - x_k}{\delta}$$

where  $\dot{x}|_{t_k}$  is the derivative of x(t) calculated at time  $t_k = k\delta$ ,  $\delta = t_{k+1} - t_k$  is the sampling interval,  $k \in \mathbb{Z}$ , and  $x_k = x(k\delta)$ ,  $x_{k+1} = x((k+1)\delta)$  are the value of x(t) at  $t_k = k\delta$ ,  $t_{k+1} = (k+1)\delta$ . This is the so called forward rectangular rule, and leads to the following expression

$$x_{k+1} = x_k + \delta f(x_k).$$

There exists also a backward rectangular rule

$$\dot{x}(k) \simeq \frac{x_k - x_{k-1}}{\delta}$$

leading to

$$x_{k+1} = x_k + \delta f(x_{k+1}).$$

Another method is the trapezoidal rule, where eventually one gets

$$x_{k+1} = x_k + \frac{\delta}{2} (f(x_k) + f(x_{k+1}))$$

These approximations can be used in place of the derivatives that appear in the controller differential equations, to obtain difference equations repetitively solved with time steps of length  $\delta$ . In the following we will consider the Euler's rule, for the sake of clarity, but the same arguments can be used with the other integration methods.

When dealing with the classical proportional, integral, and derivative control actions

$$u_p(t) = k_p e(t), \qquad u_i(t) = \frac{k_p}{T_i} \int_0^t e(\tau) d\tau, \qquad u_d(t) = k_p T_d \dot{e}(t)$$

with  $k_p$  the proportional gain,  $T_i$  the integral time,  $T_d$  the derivative time, they can be approximated with the following algebraic relations, which can be implementable with digital computers

$$u_{p,k} = k_p e_k, \qquad u_{i,k} = u_{i,k-1} + \frac{k_p}{T_i} \delta e_k, \qquad u_{d,k} = k_p T_d \frac{e_k - e_{k-1}}{\delta}$$

where  $u_{i,k}$ ,  $u_{d,k}$  are the results of the forward rule of the Euler approximation. Usually, these control actions are used together and their combination need to be done carefully. Hence, considering the Laplace transform for a classical (linear) PID controller

$$G(s) = \frac{u(s)}{e(s)} = k_p \left( 1 + \frac{1}{T_i s} + T_d s \right) e(s)$$

so that

$$su(s) = k_p \left( s + \frac{1}{T_i} + T_d s^2 \right) e(s)$$

and

$$\dot{u} = k_p \left( \dot{e} + \frac{1}{T_i} e + T_d \ddot{e} \right)$$

the Euler's method, applied twice for  $\ddot{e}$ , gives

$$u_k = u_{k-1} + k_p \left[ \left( 1 + \frac{\delta}{T_i} + \frac{T_d}{\delta} \right) e_k - \left( 1 - 2\frac{T_d}{\delta} \right) e_{k-1} + \frac{T_d}{\delta} e_{k-2} \right].$$

For linear systems (and controllers) with bandwidths of a few Hz, sample rates are often on the order of 100 Hz, so that  $\delta$  is on the order of  $10^{-2}$  s, and errors from the approximation is quite small. An empirical rule is that the sample rate should be faster that 30 times the bandwidth in order to assure that the digital controller can be made to closely match the performance of the continuous controller. Except

Shannon rule, regarding the aliasing problem, there is not a theoretic rule to fix  $\delta$  in order to ensure this close match.

The absence of a systematic rule to choose the sampling period  $\delta$  is even more problematic for nonlinear systems. In fact, it is well-known that nonlinear systems can experience a finite escape times, which roughly means that the state can go to infinity in finite time intervals [8]. This is a great difference with linear systems, where the state can go to infinity asymptotically, namely when time goes to infinity. As a result, from a conservative point of view, the controllers need to be implemented with the fastest sampling time.

With this important observation in mind, the controllers (3), (5), (6), containing PI terms, can be implemented as follows.

#### Digital implementation of the pressurizer water level controller (3)

$$\begin{split} I_{e_{lpr},k+1} &= I_{e_{lpr},k} + \delta(l_{pr,k} - l_{pr,\text{ref},k}) \\ m_{in,k} &= \frac{A_{pr}}{\psi(M_{pc,k}, T_{pc,k})} \bigg[ - \left( k_p(l_{pr,k} - l_{pr,\text{ref},k}) + k_i I_{e_{lpr},k} \right) \varphi^2(T_{pc,k}) + m_{out}^{\circ} \varphi(T_{pc,k}) \\ &+ \frac{1}{c_{p,pc}} \bigg( \frac{2c_{r,1}}{M_{pc,k}} \varphi^2(T_{pc,k}) + \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} \bigg|_k \bigg) \bigg( c_{p,pc} m_{out}^{\circ} \mathcal{A}^{\circ} + c_{\psi} N_k - n_{sg} k_{t,sg}(T_{pc,k} - T_{sg,k}) - W_{loss,pc}^{\circ} \bigg) \bigg] \end{split}$$

(7)

with  $k_p, k_i > 0$ ,

-

-

$$\begin{split} \psi(M_{pc,k},T_{pc,k}) &= \varphi(T_{pc,k}) - (T_{pc,i}^{\circ} - T_{pc,k}) \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} \bigg|_{k} - \frac{2c_{r,1}A_{pr}}{M_{pc,k}} (T_{pc,i}^{\circ} - T_{pc,k})\varphi^{2}(T_{pc,k}) \\ \varphi(T_{pc,k}) &= c_{\varphi,0} + c_{\varphi,1}T_{pc,k} - c_{\varphi,2}T_{pc,k}^{2} \\ \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} \bigg|_{k} &= c_{\varphi,1} - 2c_{\varphi,2}T_{pc,k}. \end{split}$$

Digital implementation of the pressurizer pressure controller (5)

$$\begin{split} \hat{T}_{pr,k+1} &= \hat{T}_{pr,k} + \delta \bigg[ - \bigg( \frac{m_{pr,k}^{\circ}}{M_{pr,k}} + \frac{k_{wall}}{c_{p,pr}M_{pr,k}} \bigg) \hat{T}_{pr,k} + \frac{k_{wall}}{c_{p,pr}M_{pr,k}} T_{pr,wall,k} \\ &+ \frac{1}{c_{p,pr}M_{pr,k}} W_{heat,pr,k} + \frac{c_{p,pc}m_{pr,k}^{\circ}}{c_{p,pr}M_{pr,k}} (T_{pc,k} + \Delta^{\circ}) \bigg] \\ T_{pr,wall,ref,k+1} &= T_{pr,wall,ref,k} + \delta \bigg( \frac{k_{wall}}{c_{p,wall}} T_{pr,ref,k} - \frac{k_{wall}}{c_{p,wall}} T_{pr,wall,ref,k} + k_i I_{e_{T_{pr,wall},k}} - \frac{1}{c_{p,wall}} W_{loss,pr}^{\circ} \bigg) \\ I_{e_{T_{pr,wall},k+1}} &= I_{e_{T_{pr,wall},k}} + \delta \bigg( T_{pr,wall,k} - T_{pr,wall,ref,k} \bigg) \\ W_{heat,pr,k} &= -k_{wall} (T_{pr,wall,k} - T_{pr,wall,ref,k}) - \frac{c_{p,pr}}{c_{p,wall}} k_{wall} M_{pr,k} B^T P \bigg( \frac{I_{e_{T_{pr,wall},k}}}{T_{pr,wall,k}} - T_{pr,wall,ref,k} \bigg) \\ &+ c_{p,pr} M_{pr,k} \bigg[ \dot{T}_{pr,ref} \bigg|_k + \bigg( \frac{m_{pr,k}^{\circ}}{M_{pr,k}} + \frac{k_{wall}}{c_{p,pr}M_{pr,k}} \bigg) T_{pr,ref,k} - \frac{k_{wall}}{c_{p,pr}M_{pr,k}} T_{pr,wall,ref,k} \\ &- \frac{c_{p,pr} M_{pr,k}}{c_{p,pr}M_{pr,k}} (T_{pc,k} + \Delta^{\circ}) \bigg] \\ T_{pr,ref,k} &= \frac{c_1 + \sqrt{c_1^2 - 4c_2(c_0 - p_{pr,ref,k})}}{2c_2}, \qquad \dot{T}_{pr,ref} \bigg|_k = \frac{2\dot{p}_{pr,ref,k}}{\sqrt{c_1^2 - 4c_2(c_0 - p_{pr,ref,k})}} \end{split}$$

with  $T_{pr,wall,ref,0} = T_{pr,ref,0} - W_{loss,pr}^{\circ}/k_{wall}, M_{pr,k} = M_{pc,k} - \varphi(T_{pc,k})V_{pc,0},$

$$\begin{split} m_{pr,k}^{\circ} &= m_{in,k} - m_{out}^{\circ} - \frac{1}{c_{p,pc}M_{pc,k}} \frac{\partial \varphi(T_{pc})}{\partial T_{pc}} \Big|_{k} V_{pc,0} \Big[ c_{p,pc}m_{in,k}(T_{pc,i}^{\circ} - T_{pc,k}) + c_{p,pc}m_{out}^{\circ} \Delta^{\circ} \\ &+ c_{\psi}N_{k} - n_{sg}k_{t,sg}(T_{pc,k} - T_{sg,k}) - W_{loss,pc}^{\circ} \Big]. \end{split}$$

Digital implementation of the pressurizer pressure controller (6)

$$I_{e_{ppr},k+1} = I_{e_{ppr},k} + \delta \Big( c_0 - c_1 \hat{T}_{pr} + c_2 \hat{T}_{pr}^2 - p_{pr,ref} \Big)$$

$$\xi_{k+1} = \xi_k + \delta \Big( \hat{T}_{pr} - T_{pr,wall} - \frac{1}{k_{wall}} W_{loss,pr}^\circ - \frac{1}{k} \frac{1}{c_{p,pr} M_{pr}} C_{pr} \Big)$$

$$\hat{T}_{pr,k} = \kappa \Big( \frac{c_{p,wall}}{k_{wall}} T_{pr,wall,k} - \xi_k \Big)$$

$$C_{pr,k} = \frac{c_{p,pr} M_{pr,k}}{-c_1 + 2c_2 \hat{T}_{pr,k}} \Big( \dot{p}_{pr,ref,k} - K_p \Big( c_0 - c_1 \hat{T}_{pr,k} + c_2 \hat{T}_{pr,k}^2 - p_{pr,ref,k} \Big) - K_i I_{e_{ppr},k} \Big)$$

$$W_{heat,pr,k} = k_{wall} (\hat{T}_{pr,k} - T_{pr,wall,k}) + C_{pr,k} + \delta_{pr} \Big( c_{p,pr} m_{pr,k}^\circ \hat{T}_{pr,k} - c_{p,pc} m_{pr,k}^\circ (T_{pc,k} + \Delta^\circ) \Big)$$

where  $I_{e_{ppr},0} = 0, \xi_0 = -\hat{T}_{pr,0}/\kappa + c_{p,wall}T_{pr,wall,0}/k_{wall}$ .

## 2 Self Triggered Robust Strategies for Optimal Implementations of Control Laws on Digital Devices

The implementation of controllers with digital devices presents many advantages, but at the same time poses some issues. We have already mentioned about the fact that the implementation of control laws with zero order holders, commonly used for the digital implementation of control laws, introduce a delay and hence could bring to unstable behaviors. We have also mentioned the possibility of determining a region of practical stability of the control system. In this section we want to be more specific and consider a technique, called self triggered control, determining the sampling time so that the control system performances are preserved. The obvious property to be preserved is the asymptotic stability, which in turn means that the plant is operating safely.

One important aspect is the design of the digital controller so that the control system recovers, at least in first approximation, the same behavior of a system controlled with a continuous time controller. In fact, many authors propose nonlinear digital controllers reproducing the performances of a certain continuous controller, viz emulating the behavior of the continuous controller [34] [29], [30]. This a very popular technique relies on the simple consideration that when the (fixed) sampling period is short enough, one regains the continuous behavior. Other authors aim at designing the digital controller directly in the digital setting, imposing control performances on the digital model of the system, although nonlinear systems cannot be discretized exactly in closed form, in general. In both cases, a relevant problem arises: the determination of the sampling period. From a theoretical point of view, the sampling period is usually considered constant, namely the new control value is computed periodically at each sampling time. This helps, from a mathematical point of view, the analysis of the sampled nonlinear system, and gives some mathematical tools to solve the design problem. However, it is clear that a better solution should be that of calculating the controller only "when necessary". This clearly complicates the problem from an analytical point of view. But there are also practical aspects that push to deal with variable sampling. A first aspect is that a constant sampling is quite inefficient (in terms of CPU usage, communication bandwidth, energy, etc.), since it has to be considered the worst-case scenario. In fact, since the system dynamics are nonlinear, one has to ensure good performance for all the operative

points. Incidentally, this reveals the need of criteria to fix the sampling time value, that otherwise has to be fixed using (possibly extensive) simulations, or considering empirical rules (20 times the system bandwidth [20]). A further aspect is that many digital controller perform various tasks at the same time. This is quite typical, especially in the case of embedded systems. An example is the electronic central unit in an automobile, which has to manage different tasks, with different priority. Their scheduling is clearly of critical importance to prevent negative coupling effects of lower priority tasks when computing high level tasks, such as attitude control laws. Another important example are the networked systems, where not only the processor time is a resource to be optimized, but also the available communication bandwidth is limited. In wireless sensor networks, furthermore, an important issue is the minimization of the power consumption, in order to augment the life span of the network. In all these applications, the energy consumption is related to the frequency of measurements and transmission over the network. It is clear that in these cases measurement/computation/actuation data transmission should be minimized and should occur only "when necessary".

Among the various techniques proposed to face this problem, the event triggered technique seems to be promising [21], [31], [14], [22]. This technique formalize the statement "when necessary": the measurement/computation/actuation data transmission event occurs when the state of the system assumes certain values. Clearly, this technique requires the continuous measurement of the state. To circumvent this drawback, self–triggered techniques have been proposed. In this case the controller determines its next execution time, and does not require continuous measurements of the state. In particular, when the stabilization of the system origin is considered, this event is triggered only when the asymptotic stability property, as formalized by the Lyapunov approach, can be lost [14], [4], [13], [36], [37], [5], [18], [6]. This approach can be also generalized to a weaker property such as safety [6].

Self triggered control strategies have been introduced in [33], where a heuristic rule is provided to self-trigger the next execution time of a control task on the basis of the last measurement of the state. In [11], [12], a robust self triggered strategy is proposed, which guarantees that the  $\mathcal{L}_2$  gain of a linear time invariant system is kept under a given threshold. In [13] a self triggered strategy distributed over a wireless sensor network is proposed for linear time invariant systems.

In [14] sufficient conditions for the existence of a stabilizing event-triggered control strategy are given for nonlinear systems. In [5] the authors propose a self-triggered emulation of the event-triggered control strategy proposed in [14]. In particular a methodology for the computation of the next execution time as a function of the last sample is presented, under a homogeneity condition.

In this deliverable, a methodology for the computation of the next execution time is proposed, based on polynomial approximations of Lyapunov functions, and relying on the assumption that the nonlinear differential equations and the control law are  $C^{\ell}$  functions, with  $\ell$  sufficiently large. This assumption is verified in the present case. The next sampling time is also computed in the presence of bounded sensing/computation/actuation delays and of norm-bounded parameter uncertainties and disturbances. Moreover, under weaker conditions than those used in [14], it is proved the existence of a self triggered strategy keeping the state in a "safe set" arbitrarily close to the equilibrium point, and a methodology for computing the next execution time is provided. Fixed a  $\delta$ -ball of the equilibrium point and a disturbance that is upper bounded in norm by a class  $\mathcal{K}$  function  $v(\delta)$ , a methodology is presented for the computation of the next execution time that depends on the  $\delta$  boundary defining the safe set.

#### 2.1 **Problem Formulation**

Consider a generic nonlinear system

$$\dot{x} = f(x, u, \mu, d) \tag{10}$$

where  $x \in \mathcal{D}_x \subset r^n$ ,  $\mathcal{D}_x$  a domain containing the origin,  $u \in \mathcal{D}_u \subset r^p$ ,  $\mu$  is a parameter uncertainty vector varying in a compact set  $\mathcal{D}_\mu \subset r^r$ , with  $0 \in \mathcal{D}_\mu$ , d is an external bounded disturbance vector taking values in a compact set  $\mathcal{D}_d \subset r^s$ , with  $0 \in \mathcal{D}_d$ . In the following, we may refer to (10) as the perturbed system. Furthermore, we define the nominal (or "unperturbed") system associated to the "perturbed" system (10) as

$$\dot{x} = f_0(x, u) \doteq f(x, u, 0, 0).$$

(11)

Given a state feedback control law  $\kappa: \mathcal{D}_x \to \mathcal{D}_u$ , the closed loop perturbed system is

$$\dot{x} = f(x, \kappa(x), \mu, d) \tag{12}$$

and the closed loop nominal system is

$$\dot{x} = f_0(x, \kappa(x)). \tag{13}$$

We will denote by x(t),  $t \ge t_0$ , the solution of the closed loop system (12) (or (13), according to the context), with initial condition  $x_0 = x(t_0)$ . Given a state feedback control law  $\kappa$  it is well–known that, if  $\kappa$  locally stabilizes the origin of system (13) and if  $f_0(x, \kappa(x)) \in C^{\ell}(\mathcal{D}_x)$ ,  $\ell > 1$  integer, then there exists a Lyapunov function V(x) of class  $C^1(\mathcal{D}_x)$  such that

$$\alpha_{1}(||x||) \leq V(x) \leq \alpha_{2}(||x||)$$

$$\frac{\partial V(x)}{\partial x} f_{0}(x, \kappa(x)) \leq -\alpha_{3}(||x||)$$

$$\left\| \frac{\partial V(x)}{\partial x} \right\| \leq \alpha_{4}(||x||)$$

(14)

with  $\alpha_1, \alpha_2, \alpha_3, \alpha_4 \in \mathcal{K}$  [8], [10], [35].

Moreover, given a state feedback control law  $\kappa$ , we say that system (12) is safe with respect to the set  $S \subseteq D_x$  for the time interval  $T \subseteq r_0^+$ , if  $x(t) \in S$ ,  $\forall t \in T$ .

The feedback control signal  $u(t) = \kappa(x(t))$  requires continuous measurements of the state of the system. We assume that state measurements are available at sampling times  $t_k$ , which define a sequence  $I = \{t_k\}_{k\geq 0}$ , and that the applied control is

$$u_{\mathcal{I}}(t) = \begin{cases} 0 & \forall t \in [t_0, t_0 + \Delta_0) \\ \kappa(x_k) & \forall t \in [t_k + \Delta_k, t_{k+1} + \Delta_{k+1}), \ k \ge 0 \end{cases}$$

(15)

where  $\{\Delta_k\}_{k\geq 0}$  is a sequence of delays, due to the transmission time from the sensor to the controller, the computation time, and the transmission time from the controller to the actuator. On the basis of this assumption, we address the following problems.

**Problem 1** Given a system (11), and a state feedback control law  $\kappa$  such that the origin of (13) is asymptotically stable with region of attraction  $\Omega \subset \mathcal{D}_x$  containing the origin, determine a function  $\tau_s : \mathcal{D}_x \to [\tau_{\min}, \infty), \tau_{\min} > 0$  and a maximum allowed delay  $\Delta_{\max} \in [0, \tau_{\min}]$  such that if the sequence of sampling instants I is inductively defined by

$$t_{k+1} = t_k + \tau_s(x_k)$$

(16)

and if the delays are such that

$$\Delta_k \in [0, \Delta_{\max}), \quad \forall \, k \ge 0, \tag{17}$$

then the origin of the closed loop system (13) with control input signal  $u_I(t)$  as in (15) is asymptotically stable with region of attraction  $\Omega$ .

**Problem 2** Given a system (10) (resp. (11)), and a state feedback control law  $\kappa$  such that the origin of (12) (resp. (13)) is asymptotically stable with region of attraction  $\Omega \subset \mathcal{D}_x$  containing the origin, and an arbitrary safe set  $\mathcal{B}_{\delta} = \{x \in r^n \mid ||x|| < \delta\} \subset \Omega, \ \delta > 0$ , determine  $\tau_s$  and  $\Delta_{\max}$  as defined in Problem 1 such that if I is inductively defined by (16) and if  $\Delta_k$  satisfies (17), then the closed loop system (12) with control input signal  $u_I(t)$  as in (15) is safe with respect to  $\mathcal{B}_{\delta}$  for the time interval  $[t_0, \infty)$ .

In Problems 1 and 2, the function  $\tau_s$  is used to determine the next sampling instant as a function of the current measurement of the system. The purpose is to obtain a self triggered control system that is robust with respect to delays bounded by a design parameter  $\Delta_{\text{max}}$ . By choosing the next sampling instant  $t_{k+1}$  as a function of the current measurement at time  $t_k$ , we perform sampling only when needed for guaranteeing asymptotic stability or safety. The aim is to determine a sampling instant sequence I such that the intersampling time  $t_{k+1} - t_k$  is as large as possible, in order to reduce transmission power of the sensing and actuation data transmissions, and to reduce the CPU effort due to the computation of the control.

As a comparison of the above definitions with the concepts of Maximally Allowable Transmission Interval (MATI) and Maximally Allowable Delay (MAD) introduced in [7], we can interpret  $\Delta_{max}$  as the (global) MAD, and  $t_{k+1} - t_k = \tau_s(x_k) - t_k$  as the (local) MATI of the system in the time interval [ $t_k, t_{k+1}$ ] on the basis of the measurement  $x_k = x(t_k)$  of the state x(t) at  $t = t_k$ .

#### 2.2 Self Triggered Stabilizing Control

The results developed in this section address Problem 1 for system (11), and are based on the following assumptions, which are weaker than those required in [5] (viz., homogeneity of the closed loop dynamics) to compute the next sampling time as a function  $\tau_s$  of the current state of the system.

#### Assumption 1 Assume that

- 1.  $f_0 \in C^{\ell}(\mathcal{D}_x \times \mathcal{D}_u)$ , with  $\ell$  a positive integer sufficiently large;

- 2. There exists a nonempty set  $\mathcal{U}$  of state feedback laws  $\kappa: \mathcal{D}_x \to \mathcal{D}_u$ , such that  $\kappa \in C^{\ell}(\mathcal{D}_x)$  and the origin of (13) is asymptotically stable, with region of attraction a certain compact  $\Omega \subset \mathcal{D}_x$ containing the origin;

- 3. The functions  $\alpha_3, \alpha_4 \in \mathcal{K}$  in (14) are such that  $\alpha_3^{-1}, \alpha_4$  are Lipschitz.

The assumption of existence of a stabilizing control (i.e. non-emptiness of the set  $\mathcal{U}$ ) is not restrictive, since if the nominal system cannot be stabilized using continuous time measurement and actuation, then it is clear that the nominal system cannot be stabilized using a digital control with zero-order holders. The main limitation of Assumption 1 is the Lipschitz condition on  $\alpha_3^{-1}(\cdot)$  and  $\alpha_4(\cdot)$ . We will show how to weaken this assumption in Section 2.3, which will be devoted to safety control.

**Theorem 1** Under Assumption 1, Problem 1 is solvable for system (11), and the function  $\tau_s$  can be iteratively computed as a function of the current state of the system and the maximum allowable delay  $\Delta_{\text{max}}$ .

*Proof:* We first prove the result for  $\Delta_k = 0$ . Since  $\mathcal{U}$  is not empty, by Assumption 1, we pick a state feedback control law  $\kappa \in \mathcal{U}$ . Since  $f_0(x, \kappa(x)) \in C^{\ell}(\mathcal{D}_x)$  with  $\ell > 1$ , there exists a Lyapunov candidate

V(x) that satisfies (14). Choose r > 0 such that the ball  $B_r = \{x \in \Omega : ||x|| \le r\} \subset \Omega$ . For  $x_k \in B_r$ ,

$$\dot{V} = \frac{\partial V}{\partial x} f_0(x, \kappa(x_k)) = \frac{\partial V}{\partial x} f_0(x, \kappa(x)) + \frac{\partial V}{\partial x} \Big( f_0(x, \kappa(x_k)) - f_0(x, \kappa(x)) \Big)$$

$$\leq -\alpha_3(||x||) + \alpha_4(||x||) ||d_h||$$

(18)

where

$$d_{h} = f_{0}(x(t), \kappa(x_{k})) - f_{0}(x(t), \kappa(x(t)))$$

can be considered as a perturbation due to the holding.

Under Assumption 1, there exists a  $\delta_k > 0$  such that  $\dot{x} = f(x, \kappa(x_k))$  has a unique solution over  $[t_k, t_k + \delta_k]$ . Hence, we can expand the components  $d_{h,i}$  of  $d_h$  in Taylor series. Consider the  $i^{th}$  component  $d_{h,i}$ ,  $i = 1, \dots, n$ , of the *n*-dimensional vector  $d_h$ . One can expand each component in Taylor series with respect to  $t \in [t_k, t_k + \delta_k]$ , on the right of  $t_k$ , up to the  $2^{nd}$  term, with Lagrange remainder of the  $3^{rd}$  term

$$d_{h,i} = \varphi_{1,i}(x_k)(t - t_k) + \varphi_{2,i}(\bar{x}_i, x_k)(t - t_k)^2$$

(19)

where

$$\varphi_{1,i}(x_k) = d_{h,i}\Big|_{x(t)=x_k}, \ \varphi_{2,i}(\bar{x}_i, x_k) = \frac{1}{2} \left. \frac{\mathrm{d}_+^2 d_{h,i}}{\mathrm{d}t^2} \right|_{x(t)=\bar{x}_i}$$

where  $\frac{d_{+}^{n}(\cdot)}{dt^{n}}$  denotes the *n*-th right derivative. According to Taylor theorem with Lagrange remainder, there exists  $\bar{t}_{i} \in [t_{k}, t]$ , with  $\bar{x}_{i} = x(\bar{t}_{i})$ ,  $i = 1, \dots, n$ , such that the equality (19) holds. Hence,

$$||d_h|| \le ||\varphi_1(x_k)||(t - t_k) + ||\varphi_2(\bar{x}, x_k)||(t - t_k)^2$$

where  $\bar{x} \doteq (\bar{x}_1, \cdots, \bar{x}_n)$  and

$$\varphi_1(x_k) \doteq \left(\varphi_{1,1}(x_k), \cdots, \varphi_{1,n}(x_k)\right)^T$$

$$\varphi_2(\bar{x}, x_k) \doteq \left(\varphi_{2,1}(\bar{x}_1, x_k), \cdots, \varphi_{2,n}(\bar{x}_n, x_k)\right)^T.$$

Consider the set  $\Omega_{V(x_k)} \doteq \{x \in \Omega : V(x) \le V(x_k)\}$ , and define

$$M_1(x_k) \doteq ||\varphi_1(x_k)||, \qquad M_2(x_k) \doteq \max_{\bar{x} \in \mathcal{Q}_{V(x_k)}} ||\varphi_2(\bar{x}, x_k)||.$$

Since  $f, \kappa \in C^{\ell}$  and  $\Omega_{V(x_k)}$  is compact, then  $M_1(x_k)$  is finite for any  $x_k \in \Omega_{V(x_k)}$ , and  $M_2(x_k) \in r^+$  exists and is finite for any  $x_k \in \Omega_{V(x_k)}$ .

Note that there exists a time interval  $[t_k, t_{k+1} < t_k + \delta_k]$  such that

$$\alpha_4(||x||)||d_h|| \le \vartheta \alpha_3(||x||) \tag{20}$$

is satisfied for a fixed  $\vartheta \in (0, 1)$ . In fact, (20) is satisfied if

$$\alpha_3^{-1}\left(\frac{1}{\vartheta}\alpha_4(||x||)\left(M_1(x_k)(t-t_k)+M_2(x_k)(t-t_k)^2\right)\right) \le ||x||$$

Since  $\alpha_3^{-1}$  and  $\alpha_4$  are Lipschitz, then equation (20) is satisfied if

$$\frac{1}{\vartheta} L_{\alpha_3^{-1}} L_{\alpha_4} \| x \| \Big( M_1(x_k)(t - t_k) + M_2(x_k)(t - t_k)^2 \Big) \le \| x \|$$

where  $L_{\alpha_3^{-1}}, L_{\alpha_4} > 0$  are the Lipschitz constants of  $\alpha_3^{-1}$ ,  $\alpha_4$ , respectively. The above equation directly implies that (20) is satisfied if

$$M_1(x_k)(t - t_k) + M_2(x_k)(t - t_k)^2 \le \frac{\vartheta}{L_{\alpha_3^{-1}}L_{\alpha_4}}.$$

(21)

Hence, if we define

$\tau_s(x_k) \doteq \max \{ t - t_k : (21) \text{ is satisfied for each } t - t_k \in [0, \tau_s(x_k)] \}$  $\tau_{\min} \doteq \min_{x_k \in \mathcal{Q}_{V(x_k)}} \tau_s(x_k)$

and we choose  $t_{k+1} = t_k + \tau_s(x_k)$ , then  $\dot{V}(t) \leq -(1 - \vartheta)\alpha_3(||x||) < 0$  for all  $t \in [t_k, t_{k+1}]$  and for all  $k \geq 0$ . This implies that the origin is asymptotically stable. Equation (21) is a second degree inequality in the form  $ay^2 + by \leq c$ , where a, b are non-negative and upper bounded for each  $x_k \in \mathcal{D}_x$ , and c is strictly positive and upper bounded. This trivially implies that  $\tau_s(x_k)$  is strictly positive for each  $x_k \in \mathcal{Q}_{V(x_k)}$ , and thus  $\tau_{\min}$  is strictly positive as well. In this way,  $\tau_s(\cdot)$  remains defined iteratively for each  $k \geq 0$ . This completes the proof for  $\Delta_k = 0$ .

For the case of  $\Delta_k > 0$ , following the same reasoning

$$\dot{V}(t) = \frac{\partial V}{\partial x} f_0(x(t), \kappa(x_k)) = \frac{\partial V}{\partial x} f_0(x, \kappa(x)) + \frac{\partial V}{\partial x} (d_h + d_{\Delta_k})$$

$$\leq -\alpha_3(||x||) + \alpha_4(||x||) ||d_h|| + \alpha_4(||x||) ||d_{\Delta_k}||$$

for  $t \ge t_k + \Delta_k$  where

$d_h = f_0(x(t), \kappa(x(t_k + \varDelta_k))) - f_0(x, \kappa(x))$

$$d_{\Delta_k} = f_0(x(t), \kappa(x_k)) - f_0(x(t), \kappa(x(t_k + \Delta_k)))$$

can be considered as perturbations due to the holding and to the sensing/computation/actuation delay. Since also the solution x(t) is Lipschitz, as well as  $f_0$  and  $\kappa$ , then

$$||d_{\mathcal{A}_k}|| \le M_3 \mathcal{A}_k, \quad M_3 = L_{f_0} L_{\kappa} L_{\kappa}$$

where  $L_{f_0}$ ,  $L_{\kappa}$ ,  $L_x$  are the Lipschitz constants of  $f_0$ ,  $\kappa$ , x. Proceeding for  $d_h$  as in the previous case, we conclude that (20) is satisfied if

$$M_1(x_k)(t-t_k) + M_2(x_k)(t-t_k)^2 + M_3 \Delta_k \le \frac{\vartheta}{L_{\alpha_3^{-1}} L_{\alpha_4}}.$$

(22)

Setting  $\vartheta = \vartheta_1 + \vartheta_2$ , with  $\vartheta_1, \vartheta_2 \in (0, 1)$ , equation (22) implies that the stability condition (20) holds if

$$M_1(x_k)(t - t_k) + M_2(x_k)(t - t_k)^2 \le \frac{\vartheta_1}{L_{\alpha_3^{-1}}L_{\alpha_4}},$$

(23)

and

$$\Delta_k \le \Delta_{\max} \doteq \frac{\vartheta_2}{M_3 L_{\alpha_3^{-1}} L_{\alpha_4}}.$$

(24)

Defining

$\tau_s(x_k) \doteq \max\{t - t_k : (23) \text{ is satisfied for each } t - t_k \in [0, \tau_s(x_k)]\} - \Delta_{\max}$

$$\tau_{\min} \doteq \min_{x_k \in \mathcal{Q}_{V(x_k)}} \tau_s(x_k)$$

and if we choose  $t_{k+1} = t_k + \tau_s(x_k)$ , then  $\dot{V}(t) \leq -(1 - \vartheta)\alpha_3(||x||) < 0$  for all  $t \in [t_k + \varDelta_k, t_{k+1} + \varDelta_{\max}]$ and for all k > 0. This ensures the asymptotic stability of the origin.  $\varDelta_{\max}$  is non-negative, and for  $\vartheta_2$ sufficiently small  $t_{k+1} - t_k = \tau_s(x_k) > \varDelta_{\max} \geq 0$  for each  $x_k \in \Omega_{V(x_k)}$ . Therefore,  $\tau_{\min}$  is strictly positive as well. This completes the proof.

**Remark 1** It is worth noting that  $\tau_{\min} > 0$ , as shown in the proof, implies that the time interval between two sampling instants is lower bounded by the minimum sampling time  $\tau_{\min} > 0$ , so that undesired Zeno behaviors are avoided.

**Remark 2** The choice of  $\vartheta_1 \in (0, 1)$  corresponds to a simple tradeoff between larger intersampling times  $\tau_s(x_k)$  and robustness with respect to larger delays  $\Delta_{\max}$ . As  $\vartheta_1$  decreases,  $\tau_s(x_k)$  decreases and  $\Delta_{\max}$  increases. This implies that we improve robustness vs delays, paid by stronger sampling requirements.  $\diamond$

**Remark 3** When applying the self triggered rule defined in the above theorem in a real scenario, it is necessary to compute on-line the next sampling time for each time instant  $t_k$ . This computation corresponds to solving a second degree equality, which is reasonable in an embedded system. On the contrary, the functions  $M_1(\cdot)$  and  $M_2(\cdot)$  can be determined off-line, and then (numerically) computed on-line in  $x_k$ . However,  $M_2(\cdot)$  might be still difficult to determined in closed form. In this case, one can define

$$M_2 \doteq \max_{\bar{x}, x_k \in \Omega} \|\varphi_2(\bar{x}, x_k)\|$$

and use it in equation (21) to compute the next sampling time. This new definition clearly implies shorter sampling times.

The above remarks also apply to Theorems 2 and 3 in the following Sections.

#### 2.3 Self Triggered Safety Control

The main limitation of the results developed in Section 2.2 is the Lipschitz continuity assumption of  $\alpha_3^{-1}(\cdot)$  and  $\alpha_4(\cdot)$ . The following example shows that even exponentially stabilizable systems do not always satisfy this assumption.

**Example 1** Consider the system  $\dot{x} = Ax + Bu + f(x, u) = f_0(x, u)$  with

$$f_0(x,u) = \begin{pmatrix} -x_1 + x_2 + x_1^2 \\ (1+x_1)u \end{pmatrix}.$$

Let  $u = \kappa(x) = -x_2 \in \mathcal{U}$ . Consider the Lyapunov candidate  $V(x) = x^T P x$ , with P solution of the Lyapunov equation  $PA_c + A_c^T P = -Q$ , with Q = 2I, I the identity matrix, and  $A_c = \begin{pmatrix} -1 & 1 \\ 0 & -1 \end{pmatrix}$ . Since  $P = \begin{pmatrix} 2 & 1 \\ 1 & 3 \end{pmatrix}$ , then  $\lambda_{\min}^P \approx 1.382$  and  $\lambda_{\max}^P \approx 3.618$  denote respectively the minimum and the maximum eigenvalue of P. For  $||x|| \leq 2/3$ , the time derivative of V satisfies

$$\dot{V} = -\|x\|_Q^2 + 2|x_1|^3 + 3|x_1|x_2^2 \le -2x_1^2 - 2x_2^2 + 2(2/3)x_1^2 + 3(2/3)x_2^2 \le -\frac{1}{2}\|x\|^2$$

thus the origin is locally exponentially stable, with  $\alpha_1(||x||) = \lambda_{\min}^P ||x||^2$ ,  $\alpha_2(||x||) = \lambda_{\max}^P ||x||^2$ ,  $\alpha_3(||x||) = ||x||^2/2$ ,  $\alpha_4(||x||) = \lambda_{\max}^P ||x||$ .

It is clear that Assumption 1 is not satisfied, since  $\alpha_3^{-1}(\cdot)$  is not Lipschitz. For this reason, one the basis of the previous results, one can not ensure the existence of a stabilizing self triggered strategy.  $\diamond$

The main technical problem is that, if  $\alpha_3^{-1}(\cdot)$  is not Lipschitz, the next sampling time  $\tau_s(x_k)$  goes to zero as  $x_k$  approaches the equilibrium point, and this might generate Zeno behaviors. The results developed in this section address Problem 2, both for the nominal system (11) and the generic system (10), and are based on the following assumption, that does not require  $\alpha_3^{-1}(\cdot)$  to be Lipschitz.

**Assumption 2** Assume that  $f_0 \in C^{\ell}(\mathcal{D}_x \times \mathcal{D}_u)$ , with  $\ell$  a positive integer sufficiently large. Assume that there exists a nonempty set  $\mathcal{U}$  of state feedback laws  $\kappa: \mathcal{D}_x \to \mathcal{D}_u$ , such that  $\kappa \in C^{\ell}(\mathcal{D}_x)$  and the origin of the system (13) is asymptotically stable, with region of attraction a certain compact  $\Omega \subset \mathcal{D}_x$  containing the origin.  $\diamond$

For system (11) (unperturbed case) we determine a function  $\tau_s$  to compute the next sampling time as a function of the current state of the system and the maximum allowable delay  $\Delta_{\text{max}}$ , such that the closed loop system applying a self triggered strategy is safe. On the basis of Assumption 2, in Theorem 2 we provide a different computation of  $\tau_s$  providing less conservative (less frequent) sampling instants.

For system (10) (perturbed case), given a  $\delta$  boundary of the equilibrium point and a disturbance that is upper bounded in norm by a class  $\mathcal{K}$  function  $v(\delta)$ , we determine a function  $\tau_s$  to compute the next sampling time as a function of the current state of the system and the maximum allowable delay  $\Delta_{\text{max}}$ , such that the closed loop system applying a self triggered strategy is safe with respect to  $\delta$ . We remark that, according to well known results in [8], a locally stable system subject to a bounded disturbance always satisfies a safety property with respect to  $\delta$  sufficiently small. Nevertheless neither the computation of the function  $\tau_s$  nor the relation among the safe boundary  $\delta$  and the disturbance upper bound  $v(\delta)$  are straightforward from the results in [8].

#### 2.4 Unperturbed Systems

The following theorem states that, if a system (11) is asymptotically stabilizable using a continuous time state feedback control law, then it is always possible to keep the state arbitrarily close to the equilibrium point by applying a digital self triggered strategy. Note that, in order to guarantee that the state is *arbitrarily* close to the equilibrium point, we need the stabilizability assumption.

**Theorem 2** Under Assumption 2, Problem 2 is solvable for system (11), and the function  $\tau_s$  can be iteratively computed as a function of the current state of the system and the maximum allowable delay  $\Delta_{\text{max}}$ .

*Proof:* Using the same reasoning of Theorem 1 proof, and directly considering the case  $\Delta_k > 0$ , we conclude that the following inequality

$$\dot{V} \le -(1 - \vartheta)\alpha_3(||x||) + \alpha_4(||x||)(||d_h|| + ||d_d||) - \vartheta\alpha_3(||x||) \le -(1 - \vartheta)\alpha_3(||x||)$$

holds when

$$\alpha_4(||x||) (M_1(x_k)(t-t_k) + M_2(x_k)(t-t_k)^2 + M_3 \varDelta_k) \leq \vartheta \alpha_3(||x||)$$

with  $\vartheta \in (0, 1)$ , and  $d_h, d_A, M_1(x_k), M_2(x_k), M_3$  defined as in Theorem 1. The above inequality holds if

$$||x|| \ge \eta \doteq \alpha_3^{-1} \left( \frac{\alpha_4(\delta)}{\vartheta} \left( M_1(x_k)(t-t_k) + M_2(x_k)(t-t_k)^2 + M_3 \varDelta_k \right) \right).$$

This implies, by [8], that there exists  $b := \alpha_1^{-1}(\alpha_2(\eta)) > 0$  such that  $||x(\tau)|| \le b$ ,  $\forall \tau \in [t_k, t]$  if  $x_k \in \mathcal{B}_b$  and if the following holds

$$\alpha_4(\delta) \Big( M_1(x_k)(t - t_k) + M_2(x_k)(t - t_k)^2 + M_3 \varDelta_k \Big) \le \vartheta \alpha_3 \Big( \alpha_2^{-1}(\alpha_1(\delta)) \Big)$$

(25)

where we imposed the constraint  $b = \delta$ . Equation (25) holds if the following inequalities hold

$$\alpha_4(\delta) \Big( M_1(x_k)(t-t_k) + M_2(x_k)(t-t_k)^2 \Big) \le \vartheta_1 \alpha_3 \Big( \alpha_2^{-1}(\alpha_1(\delta)) \Big)$$

$$\alpha_4(\delta) M_3 \Delta_k \le \vartheta_2 \alpha_3 \Big( \alpha_2^{-1}(\alpha_1(\delta)) \Big)$$

(26)

where we have set  $\vartheta = \vartheta_1 + \vartheta_2$ , with  $\vartheta_1, \vartheta_2 \in (0, 1)$  and  $\vartheta_1 + \vartheta_2 < 1$ . Defining

$$\begin{split} \Delta_{\max} &\doteq \vartheta_2 \frac{\alpha_3 \left( \alpha_2^{-1}(\alpha_1(\delta)) \right)}{\alpha_4(\delta) M_3} \\ \tau_s(x_k) &\doteq \max \left\{ t - t_k : \ (26) \text{ is satisfied for each } t - t_k \in [0, \tau_s(x_k)] \right\} - \Delta_{\max} \\ \tau_{\min} &\doteq \min_{x_k \in \mathcal{B}_\delta} \tau_s(x_k) \end{split}$$

and if we choose  $t_{k+1} = t_k + \tau_s(x_k)$ , then (26) holds for all  $t \in [t_k + \Delta_k, t_{k+1} + \Delta_{\max}]$  and for all  $k \ge 0$ , with  $\Delta_{\max}$  non-negative. Since  $M_1(x_k)$ ,  $M_2(x_k)$  and  $M_3$  are non-negative and upper bounded for each  $x_k \in \mathcal{B}_{\delta}$ , and since  $\alpha_4$ ,  $\alpha_3 \circ \alpha_2^{-1} \circ \alpha_1 \in \mathcal{K}$ , then the first of (26) is a second degree inequality in the form  $ay^2 + by - c \le 0$ , where a, b are non-negative and bounded and c is strictly positive and bounded. Therefore, for  $\vartheta_2$  sufficiently small,  $t_{k+1} - t_k = \tau_s(x_k) > \Delta_{\max} \ge 0$  for each  $x_k \in \mathcal{B}_{\delta}$ , and thus  $\tau_{\min}$  is strictly positive as well. This completes the proof.

systems with a Lyapunov function fulfilling Assumption . Hence, condition (??) can be used to determine a time instant  $\bar{t}_k > t_k$ , while the application of Theorem 2 can be used to determine a value  $\delta_k$ . Hence, the next sampling time results to be  $t'_k = \bar{t}_k + \delta_k$ , which may be bigger those determined by applying only Theorem 2.

#### 2.5 Perturbed Systems

that there exists a nonempty set  $\mathcal{U}$  of state feedback laws  $\kappa: \mathcal{D}_x \to \mathcal{D}_u$ , such that  $\kappa \in C^{\ell}(\mathcal{D}_x)$  and the origin of the system (12) is asymptotically stable.  $\diamond A$  generic system (10), subject to disturbances and parameter variations, can be seen as the nominal system (11), perturbed by the term

$$d_g \doteq g(x, u, \mu, d) = f(x, u, \mu, d) - f_0(x, u) \doteq d_g.$$

(27)

Hence, (10) can be rewritten as follows

$$\dot{x} = f_0(x, u) + g(x, u, \mu, d).$$

(28)

$\diamond$

**Definition 1** Under Assumption 2, and given the perturbed system (10) and a safe set  $\mathcal{B}_{\delta}$ ,  $\delta > 0$ , we say that the perturbation (27) is  $\delta$ -admissible if there exists a state feedback control law  $\kappa \in \mathcal{U}$  and a constant  $\vartheta_g \in (0, 1)$  such that the function  $g(x, \kappa(x_0), \mu, d)$  satisfies

$$\max_{\substack{x,x_k \in \mathcal{B}_{\delta} \\ d \in \mathcal{D}_d \\ \mu \in \mathcal{D}_{\mu}}} |g(x,\kappa(x_k),\mu,d)|| \le \nu(\delta) \doteq \vartheta_g \frac{\alpha_3 \left(\alpha_2^{-1}(\alpha_1(\delta))\right)}{\alpha_4(\delta)}$$

(29)

with  $\alpha_1, \alpha_2, \alpha_3, \alpha_4$  as in (14).

The  $\delta$ -admissible perturbations are those for which the safety problem with respect to a ball  $\mathcal{B}_{\delta}$  can be solved using continuous time measurement and actuation, namely it is a necessary condition to achieve safety with respect to  $\mathcal{B}_{\delta}$  using sampled measurements and actuations. Note that in condition (1) the expression of  $\nu(\delta)$  can be explicitly computed. The following theorem states that, if a system is asymptotically stabilizable using a continuous time state feedback control law and the perturbation is  $\delta$ -admissible, then it is possible to keep the state in a boundary  $\mathcal{B}_{\delta}$  of the equilibrium point by applying a digital self triggered strategy.

**Theorem 3** Under Assumption 2, Problem 2 is solvable for system (10) for any  $\delta$ -admissible perturbation (27), and the function  $\tau_s$  can be iteratively computed as a function of the current state of the system and the maximum allowable delay  $\Delta_{\text{max}}$ .

*Proof:* Using the same reasoning as in the proof of Theorem 2, and since the perturbation is assumed  $\delta$ -admissible, we conclude that the following inequality

$$\dot{V} \le -(1 - \vartheta)\alpha_3(||x||) - \vartheta\alpha_3(||x||) + \alpha_4(||x||)(||d_h|| + ||d_d|| + ||d_g||)$$

$$\le -(1 - \vartheta)\alpha_3(||x||)$$

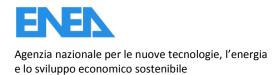

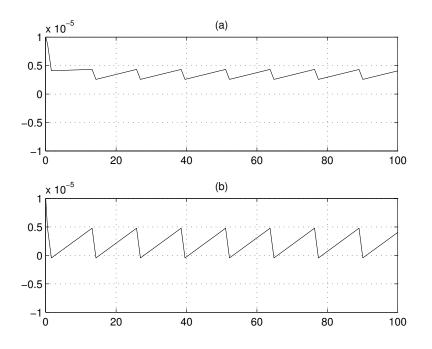

with  $d_g$  defined in (27), and  $d_h$ ,  $d_A$  defined as in Theorem 1, holds when